# République Algérienne Démocratique et Populaire Ministère de lø Enseignement Supérieur et de la Recherche Scientifique Université Mouloud MAMMERI

Faculté du Génie Électrique et de løInformatique Département døÉlectronique

#### Mémoire de fin detudes

En vue de løbtention du diplôme døingénieur døétat en électronique

**Option: Communication**

# **Thème**

Étude de la modélisation et de la simulation des phénomènes de compatibilité électromagnétique des circuits intégrés

Proposé et dirigé par :

Mr. H. KANANE

Étudié par :

Mr. KADER Amar

Mr. HASSAINE Mohammed

Année universitaire 2009/2010

#### Remerciements:

Nous souhaitons témoigner toute notre reconnaissance à notre encadrant, Mr. Hocine Kanane pour le soutien et les conseils qu'il nous a apportés durant tout notre parcours. Pour cela, nous voudrions lui adresser de chaleureux remerciements pour la confiance qu'il nous a accordée mais aussi pour son enthousiasme, sa joie de vivre et la manière unique avec laquelle il a su encadrer notre travail. Nous le remercions enfin pour l'effort de correction qu'il a apporté à ce mémoire.

Nous remercions également les membres de jury qui nous feront l'effort de juger et de critiquer notre modeste contribution afin de l'améliorer davantage.

## <u>Dédicaces :</u>

Je dédie ce travail à la mémoire de ma petite sœur RAZIKA ainsi qu'a mes parent qui n'ont eut cesse de m'encouragés et de se dépensés a fin que je réussisse mes études, un grand merci.

A mon frère et mes sœurs pour leurs soutiens et encouragements, bon courage et continuation pour vos études.

A mes Oncles Boussaâd, Ali, Said et leurs familles, vous aurais étés pour mois des exemples d'humanité, respects.

A mes cousins et cousines Marzouk, Hocine, Massinissa, Hamid, Said, Ouiza, Djegdjiga, Malika, Nacima ...

A tout mes amis

A mon ami et binôme MOHAMMED

KADER Amar

# **Dédicaces:**

Je dédie ce travail à la mémoire de mon grand-père HACENE et mon oncle MOHAMED OU RAMDAN ainsi qu'à toutes les personnes qui me sont proches et que j'aime :

- > Ma grand-mère

- ➤ Mes parents

- > Mes frères

- > Mes oncles et leurs familles

- > Mes tentes et leurs enfants

- > Mes cousins

- > Mes amis

- > A mon camarade AMAR

HASSAINE MOHAMMED

# **SOMMAIRE**

| Introduct   | ion générale                                                                 | 1  |

|-------------|------------------------------------------------------------------------------|----|

| Chapitre    | I_: Généralités sur la compatibilité électromagnétique des circuits intégrés |    |

| Introduct   | ion                                                                          | 3  |

| I) Généra   | ılités sur les circuits intégrés                                             | 3  |

| a)          | Contexte - Évolution technologique                                           | 3  |

| b)          | Historique de la circuiterie logique                                         | 4  |

| c)          | Composition d'un circuit intégré                                             | 5  |

| II) Défini  | itions préliminaires relatives à la compatibilité électromagnétique          | 7  |

| a)          | La de la compatibilité électromagnétique                                     | 7  |

| b)          | La perturbation électromagnétique                                            | 7  |

|             | Couplage en mode rayonné                                                     | 7  |

|             | Couplage en mode conduit                                                     | 7  |

| c)          | La susceptibilité et l'immunité des circuits intégrés                        | 7  |

| III) source | ces de perturbations extérieures                                             | 8  |

|             | ines des émissions parasites des circuits intégrés                           |    |

| a)          | Bruit de commutation simultanée(SSN)                                         | 8  |

| b)          | Sources d'émissions dans un circuit intégré                                  | 12 |

| V) Prop     | agation du bruit émis                                                        | 13 |

| a)          | Mécanismes de propagation conduite                                           | 13 |

| b)          | Mécanismes de couplage rayonné                                               | 15 |

| VI) Coup    | plage des perturbations externes                                             | 16 |

| VII) Effe   | ts des perturbations sur le comportement des circuits intégrés               | 17 |

| a)          | Composants analogiques                                                       | 18 |

|             | 1) Hors-bande de fréquence du composant                                      | 18 |

|             | 2) Dans la bande de fréquence du composant                                   | 18 |

| b)          | Les circuits numériques                                                      | 19 |

|             | 1) Phénomène de latchup                                                      | 19 |

|             | 2) Effet sur les sorties                                                     |    |

|             | 3) Effet sur les entrées                                                     | 19 |

| 4) Changement d'état des bascules et mémoires20                                            |  |

|--------------------------------------------------------------------------------------------|--|

| Conclusion                                                                                 |  |

|                                                                                            |  |

| Chapitre II : Modèles d'émission des circuits intégrés                                     |  |

| Introduction2                                                                              |  |

| 1                                                                                          |  |

|                                                                                            |  |

| I) Aperçu sur les méthodes de mesure de l'émission des circuits intégrés en mode rayonné21 |  |

| II) Estimation des éléments RLC24                                                          |  |

|                                                                                            |  |

| a) La résistance                                                                           |  |

| b) La capacité                                                                             |  |

| c) L'inductance26                                                                          |  |

| III) Standard IBIS et son utilisation en CEM des circuits intégrés27                       |  |

| a) Description27                                                                           |  |

| a) Description                                                                             |  |

| c) Modèle IBIS d'une sortie                                                                |  |

| d) Limitation du modèle IBIS                                                               |  |

| e) Modèle IMIC                                                                             |  |

| c) Widdele iiviie                                                                          |  |

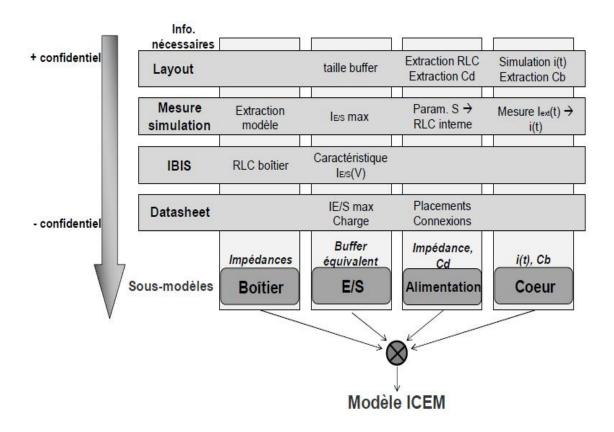

| IV) Modèle ICEM32                                                                          |  |

| a) Besoins d'un modèle de compatibilité électromagnétique32                                |  |

| 1) Format d'échange fabricant utilisateur32                                                |  |

| 2) Standard international33                                                                |  |

| 3) Utilisation dans les outils de simulation33                                             |  |

| b) Apport scientifique du modèle ICEM33                                                    |  |

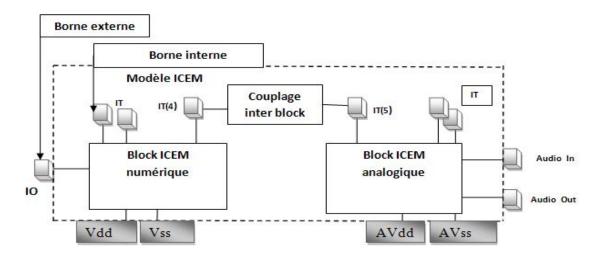

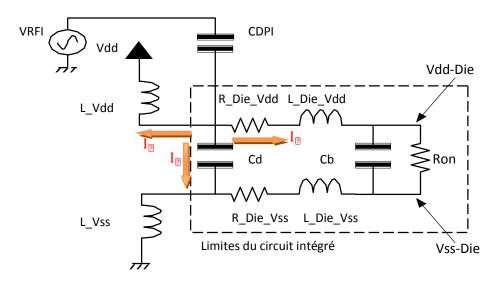

| c) Description du modèle ICEM34                                                            |  |

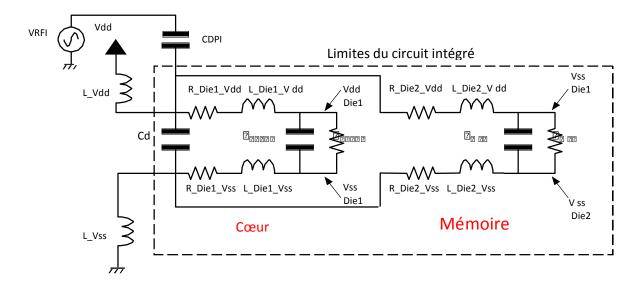

| d) Composition du modèle ICEM35                                                            |  |

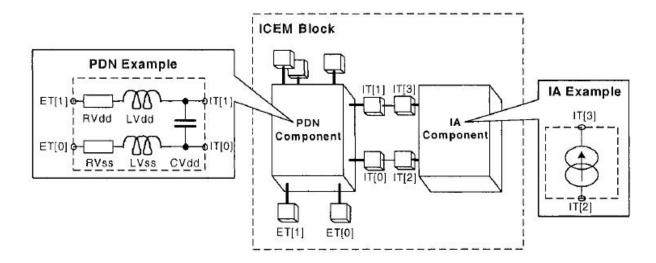

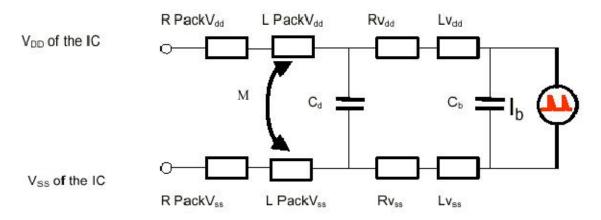

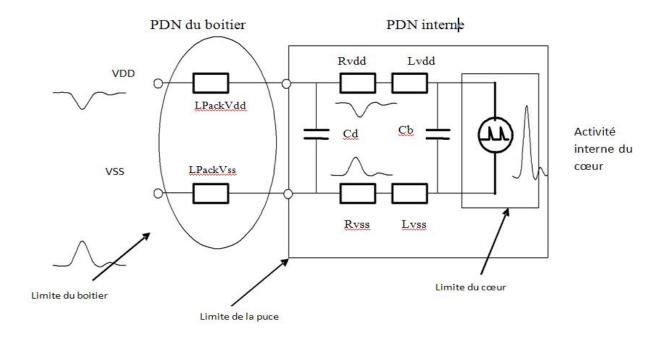

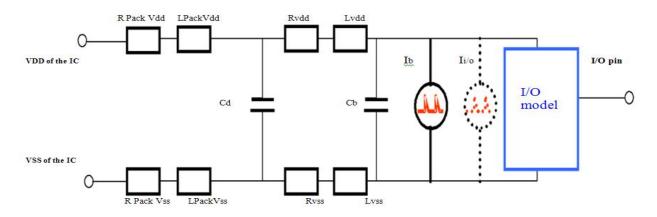

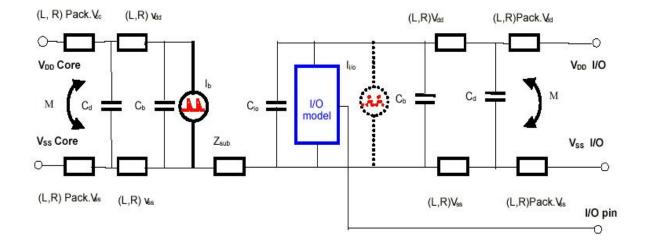

| 1) Composant PDN36                                                                         |  |

| 2) Composant IA36                                                                          |  |

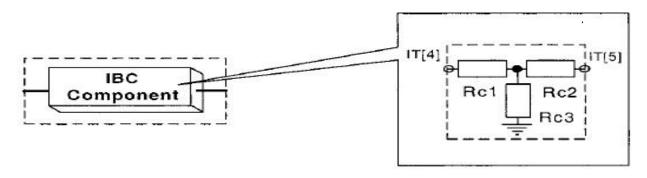

| 3) Composant IBC37                                                                         |  |

| e) Différentes formes du modèle                                                            |  |

| f) Conception du modèle ICEM                                                   | 39            |

|--------------------------------------------------------------------------------|---------------|

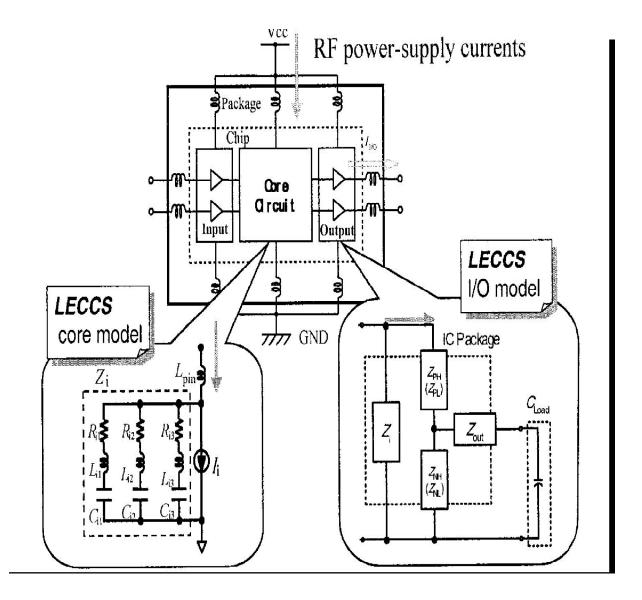

| V) Modèle LECCS                                                                | 41            |

| Conclusion                                                                     | 42            |

|                                                                                |               |

| Chapitre III : Modèles et critères de susceptibilité des circuits intégrés     |               |

| Introduction                                                                   | 43            |

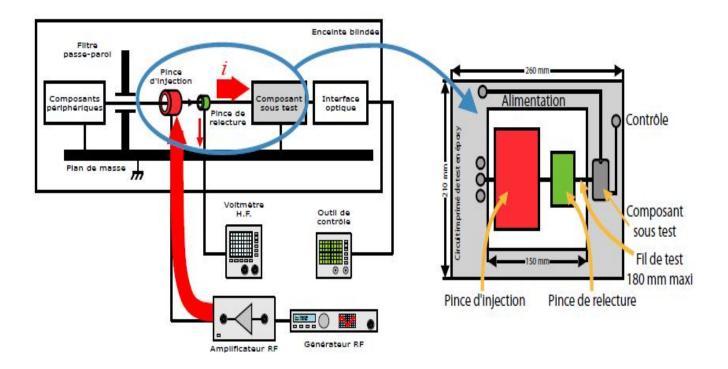

| I) Méthodes de mesure de la susceptibilité des composants en mode conduit      | 43            |

| a) Bulk Current Injection (BCI)                                                | 43            |

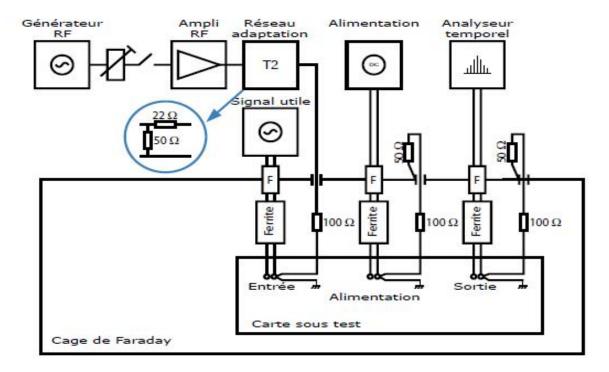

| b) Work Bench Faraday Cage (WBFC)                                              | 45            |

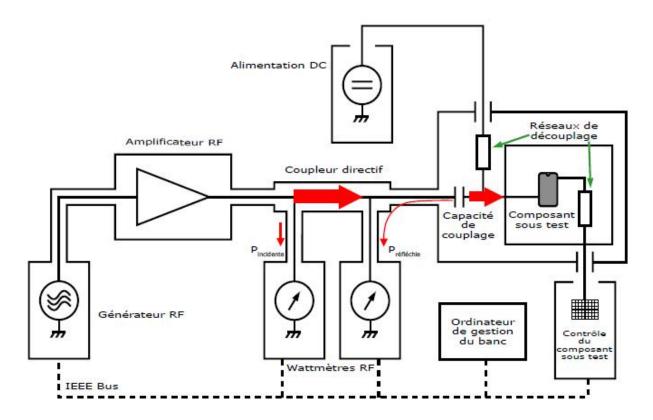

| c) Direct Power Injection (DPI)                                                | 46            |

| II) Modèle de susceptibilité des composants ICIM                               | 47            |

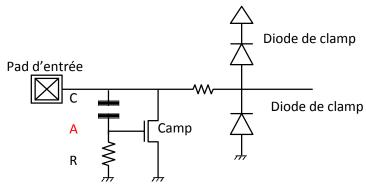

| a) Description du modèle                                                       | 48            |

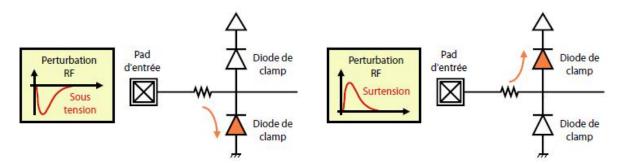

| b) Structures de protection des entrées/sorties                                | 49            |

| 1) Diodes de clamp                                                             | 49            |

| 2) Transistor NMOS à grille couplée                                            | 50            |

| 3) Modélisation des protections                                                | 50            |

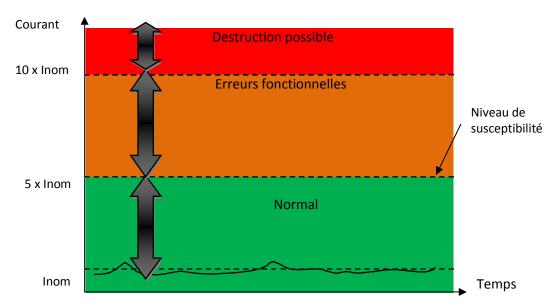

| III) Critères de susceptibilité                                                | 51            |

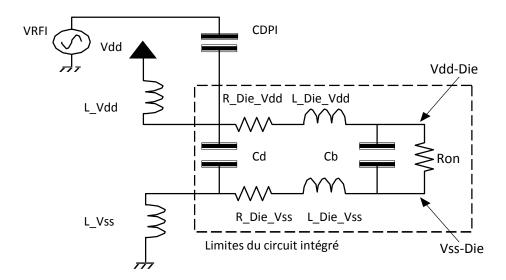

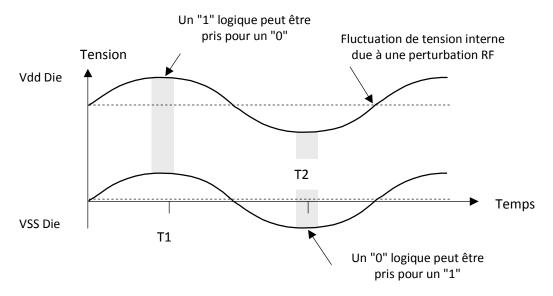

| a) Stress de l'alimentation                                                    | 51            |

| b) Diminution de la tension d'alimentation                                     | 53            |

| c) Baisse de tension différentielle                                            | 55            |

| d) Surconsommation de courant                                                  | 56            |

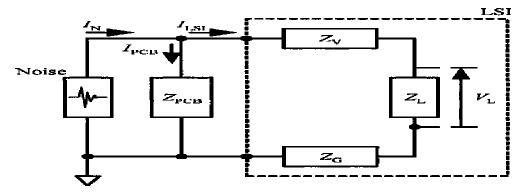

| IV) Modèle LECCS (Linear Equivalent Circuit and Current-Source models)         | 57            |

| V) Analyse de l'immunité interne                                               | 58            |

| Conclusion                                                                     | 59            |

| Chapitre IV : simulation des phénomènes de compatibilité électromagnétique ave | c le logiciel |

| <u>IC-EMC</u>                                                                  |               |

| Introduction                                                                   | 60            |

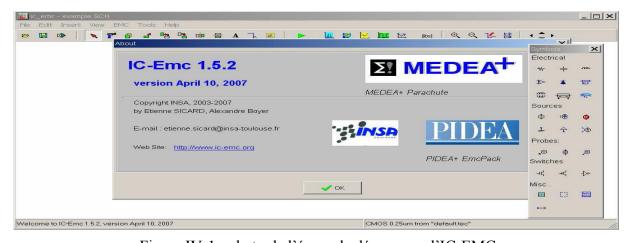

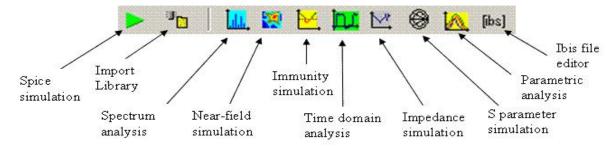

| I) Présentation du logiciel IC-EMC                                             | 60            |

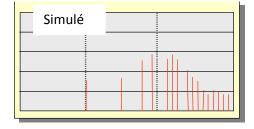

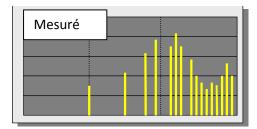

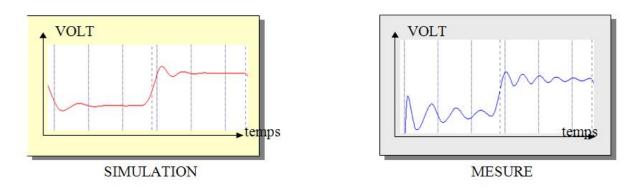

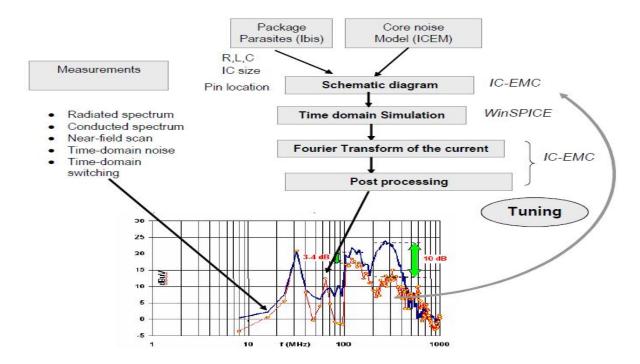

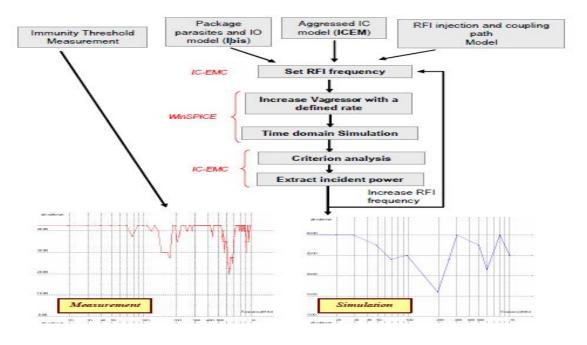

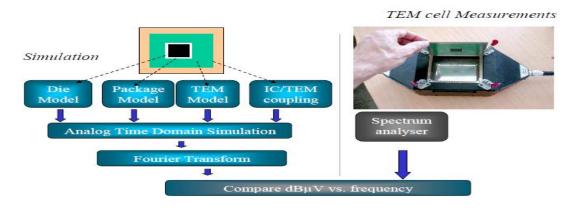

| II) Comparaison de la simulation avec la mesure                                | 61            |

| a)             | Cas de             | l'émission                                                                                          | 61             |

|----------------|--------------------|-----------------------------------------------------------------------------------------------------|----------------|

| b)             | Cas de             | e l'immunité                                                                                        | 61             |

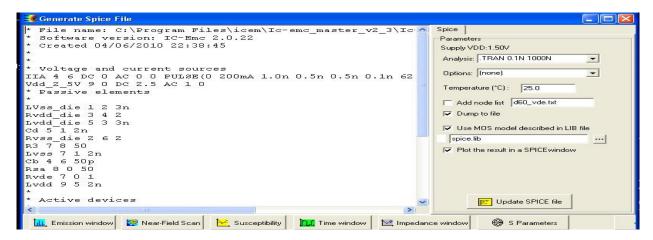

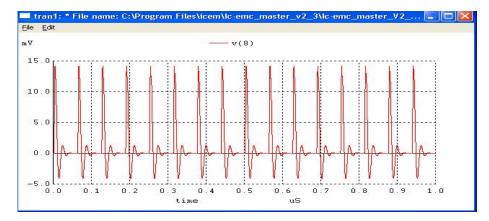

| III) Si        | imulatio           | on de l'émission                                                                                    | 62             |

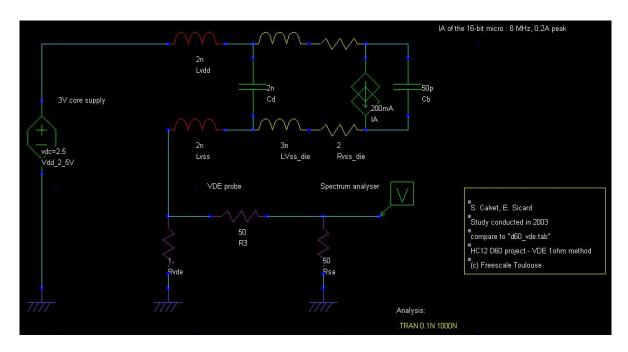

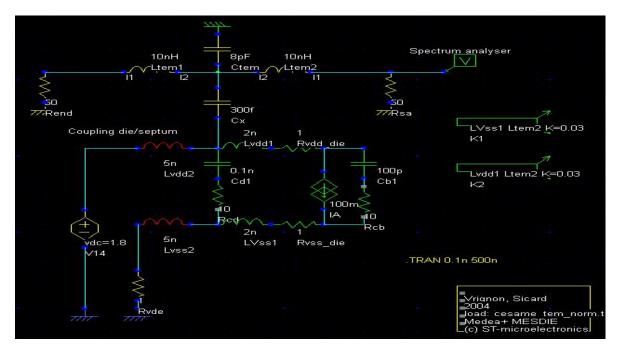

| a)             | Cas de             | e l'émission conduite (microcontrôleur HC12D60)                                                     | 62             |

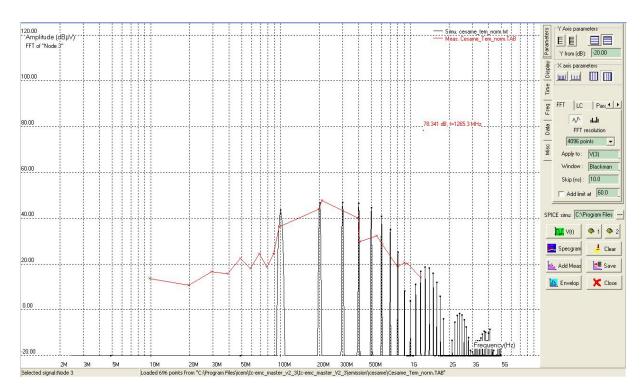

| b)             | Cas de             | e l'émission rayonné                                                                                | 65             |

|                | 1)                 | La puce CESAME                                                                                      | 65             |

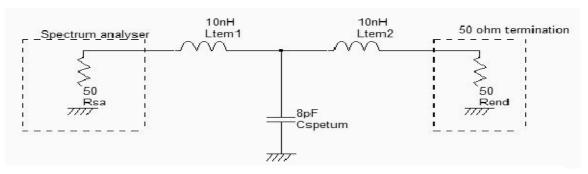

|                | ,                  | Modèle de la cellule TEM Simulation de l'émission rayonnée par la cellule CESAM dans la cellule TEM |                |

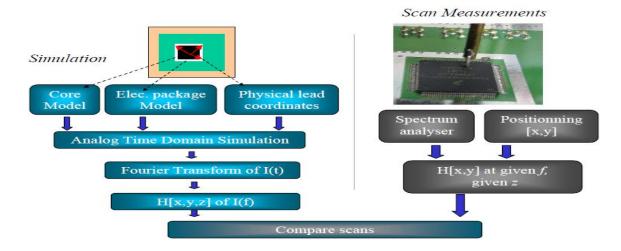

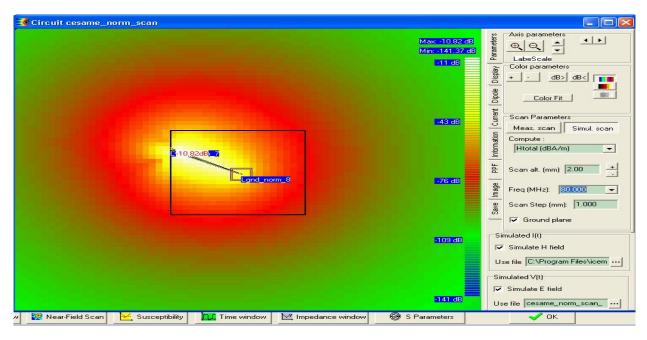

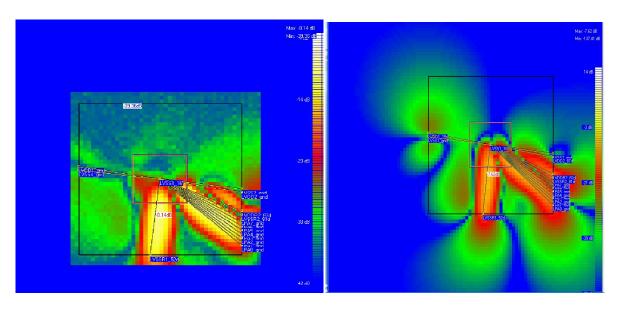

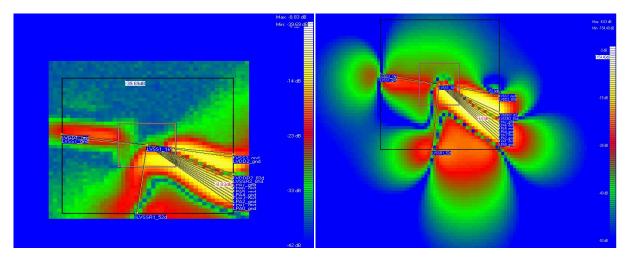

| c)             | Cas du             | balayage du champ magnétique émis en champ proche                                                   |                |

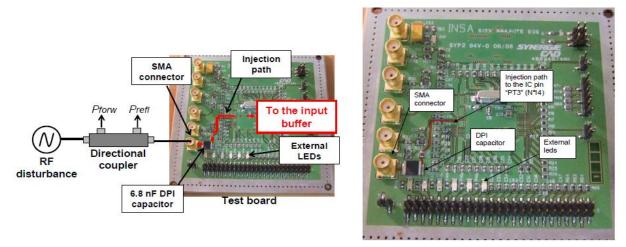

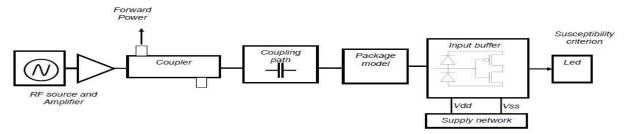

| IV) Si         | mulatio            | n de l'immunité                                                                                     | 70             |

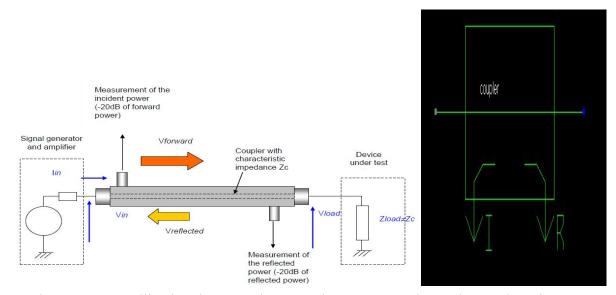

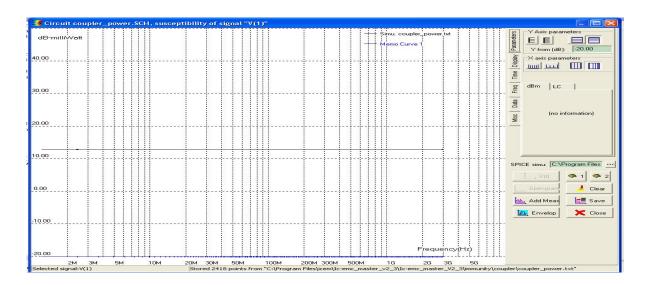

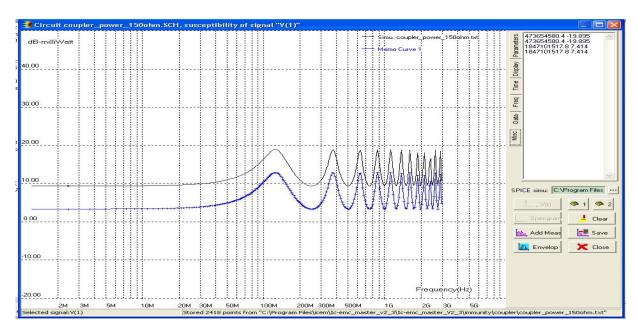

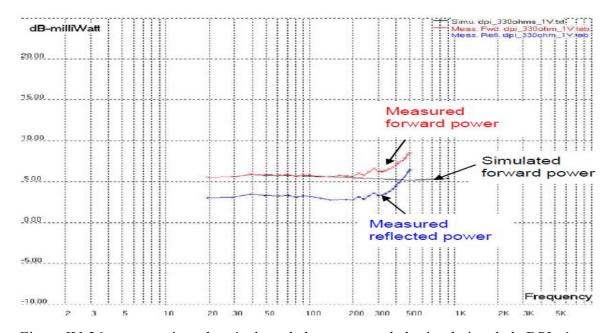

| a)             | Mesure             | e de puissance –modèle du coupleur directif                                                         | 70             |

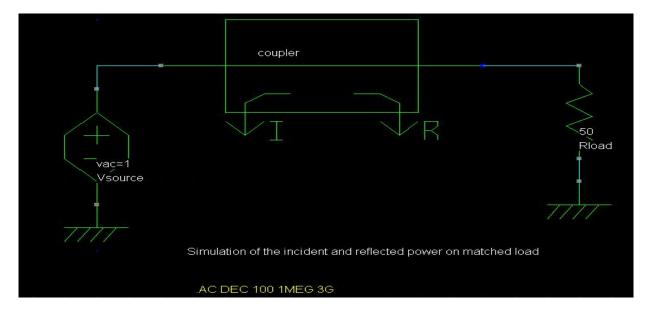

| b)             |                    | tion du coupleur dans le cas d'une charge adaptée et inadaptée                                      |                |

|                |                    | Charge adaptée                                                                                      |                |

|                | 2)                 | Charge non adaptée                                                                                  | 72             |

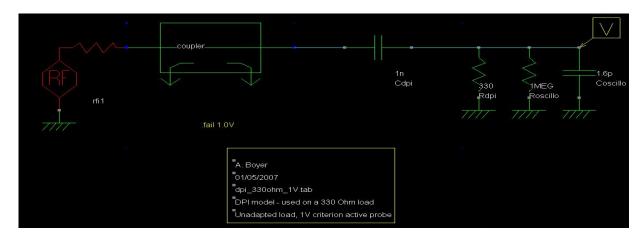

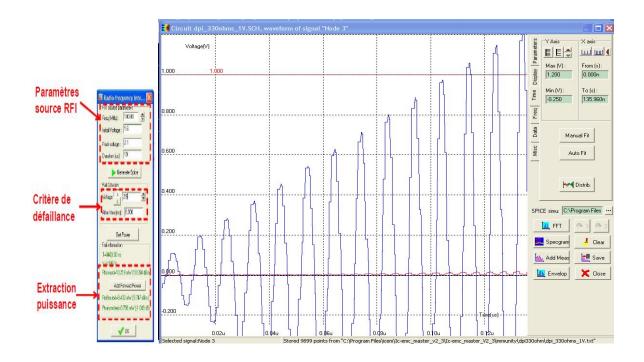

| c)             | Simula             | ation de la DPI dans le cas d'une résistance de charge de 330 $\Omega$                              | 72             |

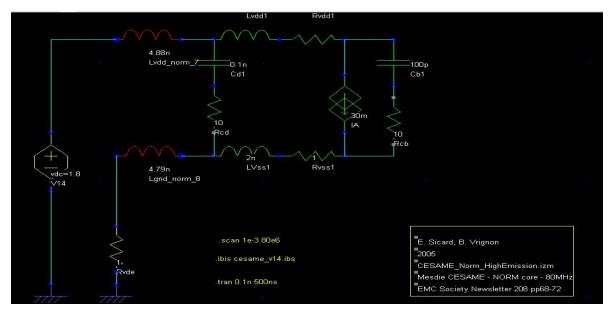

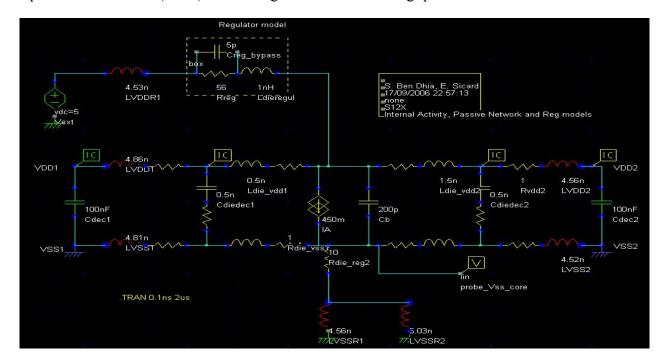

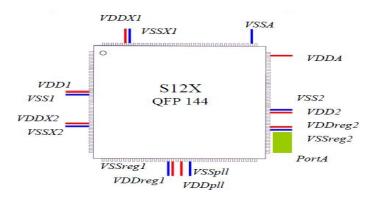

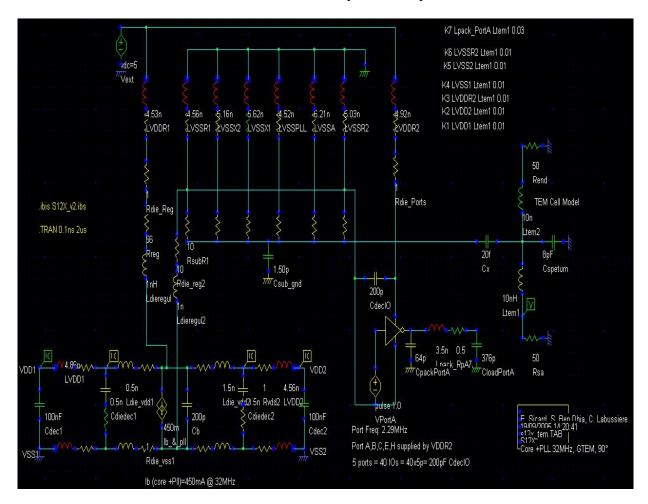

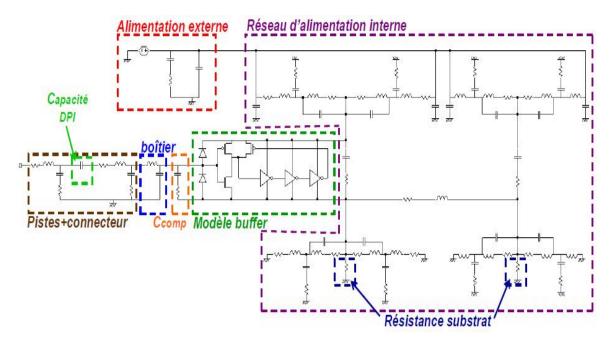

| V) Élu         | ıde du c           | as du microcontrôleur S12X                                                                          | 74             |

| a)<br>b)<br>c) | Modèle<br>1)<br>2) | u sur le microcontrôleur S12X                                                                       | 75<br>75<br>76 |

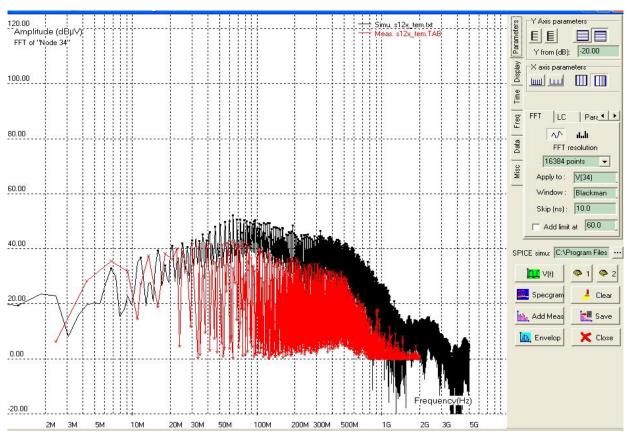

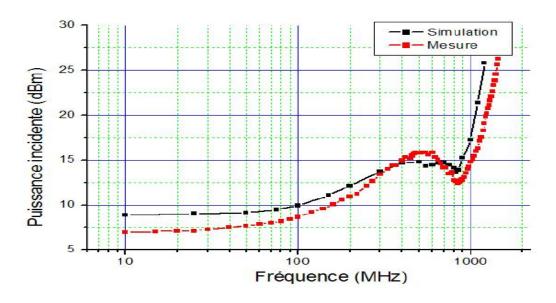

| d)             | Simula             | ation de l'émission et comparaison avec la mesure dans une cellule TEI                              | M78            |

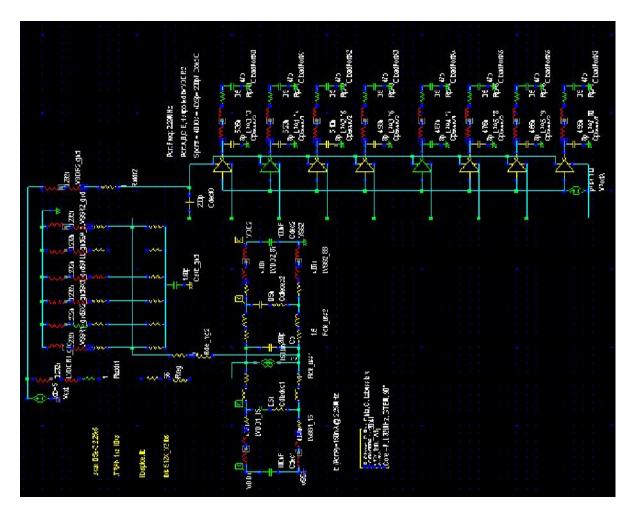

| e)             | Balaya             | ge du champ magnétique proche                                                                       | 79             |

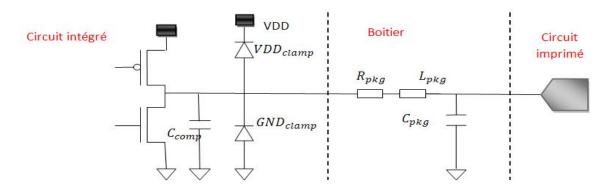

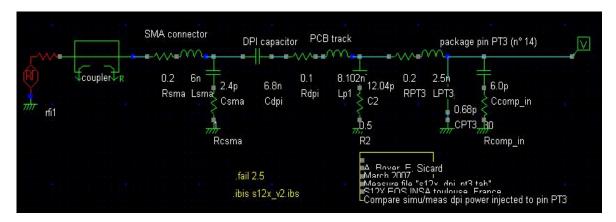

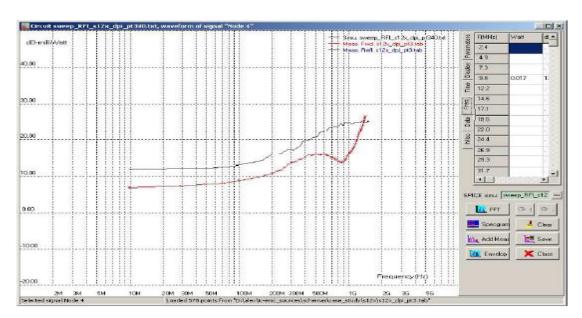

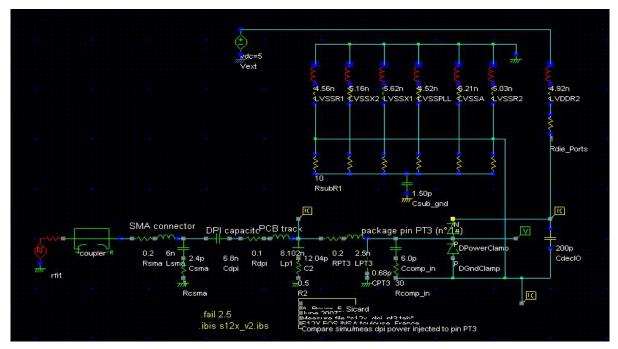

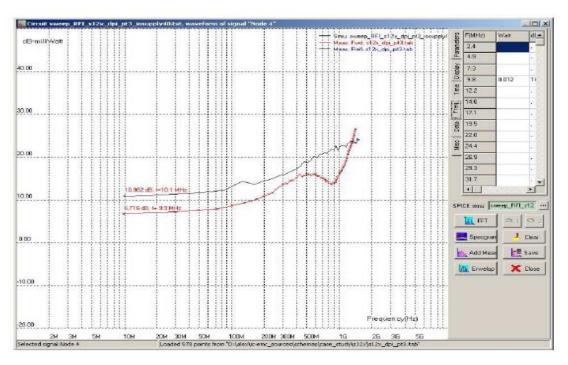

| f)             | Simula             | ation de la DPI à travers un port d'entrée/sortie                                                   | 81             |

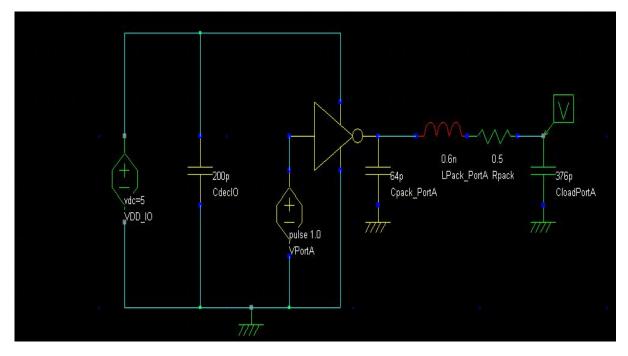

|                | 1)                 | Méthode d'agression et modèle de susceptibilité de l'entrée/sortie                                  | 81             |

|                |                    | Simulation de la susceptibilité de l'entrée/sortie en utilisant son modè                            |                |

|                | ,                  | uniquement                                                                                          |                |

|                | 3)                 | simulation de la susceptibilité de l'entrée/sortie en utilisant le PDN                              |                |

| Conal          |                    |                                                                                                     |                |

|                |                    | énérale                                                                                             |                |

|                |                    |                                                                                                     |                |

| C              | Glossaire          | 2                                                                                                   | 88             |

| Biblio         | graphie            | )                                                                                                   | 91             |

#### Résumé:

La compatibilité électromagnétique des circuits intégrés étant devenue incontournable ces dernières années, la modélisation des circuits en vu de leur simulation du point de vu de l'émission et de l'immunité vi sa vi des perturbations RF est primordiale. Les modèle ICEM et IBIS ont étés mis au point dans ce but, ICEM intégrant le modèle du cœur et IBIS celui des entrées/sorties. Le modèle de susceptibilité ICIM est lui dérivé du modèle ICEM et dédier a l'extraction des niveaux de susceptibilité des circuits par simulation.

Enfin, le logiciel IC-EMC qui est un simulateur de ces différents phénomènes se basant sur ces différents modèles nous permet de réalisé une panoplie de simulation, entre autre l'émission, le balayage du champ proche et la susceptibilité des CI.

#### **Introduction générale:**

Le 29 juillet 1967, le porte-avion américain Forrestal croisait au large des côtes du Nord-Vietnam dans le golfe du Tonkin. Alors qu'un A4-Skyhawk s'apprêtait à décoller, l'une de ses roquettes fut mise à feu accidentellement. Cette dernière fit exploser un autre appareil qui s'embrasa et détruisit à son tour l'ensemble des avions stationnés sur le pont. Le feu se propagea ensuite au stock de munitions mettant le navire hors d'usage, et nécessitant plus de 7 mois de réparation. L'accident fit 135 victimes, des centaines de blessés et plusieurs centaines de millions de dollars de dégâts. L'enquête démontra que la cause de ce fait dramatique est un pur phénomène de compatibilité électromagnétique. En effet un des RADAR du porte avion avait induit accidentellement, sur les câblages des roquettes placées sous l'avion, une tension suffisante pour activer la mise à feu de l'une d'entre elles. [lamoureux]

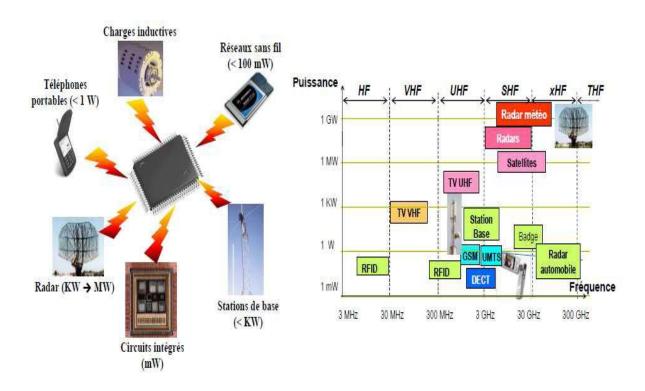

Plus qu'en 1967, aujourd'hui les circuits intégrés sont soumis à des perturbations électromagnétiques provenant de sources bien plus nombreuses et variées. L'apparition de nouveaux protocoles de communication (GSM, UMTS, etc.), l'utilisation de radar de plus en plus puissant combiné au progrès de la microélectronique qui rend les CI de plus en plus fragiles vis-à-vis de ce genre de perturbations, augmentent considérablement les risques liés aux phénomènes de comptabilité électromagnétique. A juste titre donc l'étude de ce genre de phénomènes revêt une importance capitale.

Néanmoins le problème de compatibilité électromagnétique des circuits est particulièrement difficile, puisque ceux-ci sont en évolution rapide. En outre, les nouveaux circuits intégrés imposent de nouvelles contraintes, donc les normes de leur compatibilité doivent également évoluer. Cependant, avec des tailles plus petites qu'un micron, les contraintes actuelles sont très difficiles à satisfaire et celles du futur le seront encore plus.

Dans ce mémoire nous étudions différentes méthodes de spécification de l'émission et de la susceptibilité des circuits intégrés. Pour se faire, nous verrons dans un premier chapitre un ensemble de généralités importantes si l'on veut aborder et comprendre les problèmes liés à la compatibilité électromagnétique des circuits intégrés.

Un deuxième chapitre nous renseignera notamment sur les méthodes de mesure en mode rayonné et sur les modèles utilisés pour la prédiction des émissions d'un circuit intégré, il y sera question notamment du modèle ICEM et IBIS.

Le troisième chapitre sera consacré à la CEM dans son volet immunité, les méthodes de mesure en mode conduit ainsi qu'une perspective de modèle de prédiction des niveaux de susceptibilité des circuits intégrés aux bruits électromagnétiques.

Enfin le dernier chapitre de ce travail portera sur le logiciel de simulation à savoir le IC-EMC. Il sera décrit, un ensemble de simulation de l'émission et de l'immunité pour différents composants y sera présenté. Nous terminerons ce travail par le cas du microcontrôleur S12X pour lequel la panoplie de simulations sera effectuée et les résultats comparés à ceux obtenus par mesures, pour nommer la capacité du IC-ICEM a réaliser des simulations dont les résultats sont proches des mesures sans pour autant divulguer quelques secrets que se soit sur les circuits analysés.

### **Chapitre I:**

Généralités sur la compatibilité électromagnétique des circuits intégrés

#### Introduction

De nos jours l'étude de la compatibilité électromagnétique est devenue incontournable pour l'assurance d'un bon fonctionnement des différents systèmes électroniques. En effet les systèmes électroniques sont de plus en plus exposés à ce genre de problèmes vu la multiplicité des sources de perturbations.

Ce chapitre sera consacré à un certain nombre de généralités qu'il faut connaitre afin d'aborder correctement le domaine de la compatibilité électromagnétique des circuits intégrés. Nous y ferons une synthèse non exhaustive des problèmes qu'induisent les perturbations électromagnétiques sur le fonctionnement des différents composants.

#### I) Généralités sur les circuits intégrés

#### a) Contexte - Évolution technologique

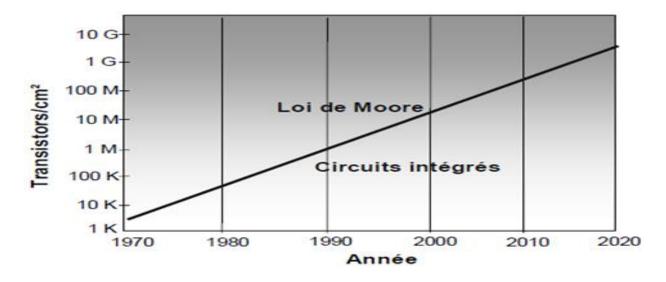

La microélectronique a connu une grande évolution ces quarante dernières années qui s'est accompagnée d'une miniaturisation exponentielle. Cette évolution suit une loi appelée loi de Moore, qui prévoit que tous les 18 mois, le nombre de transistors sur une même surface de silicium double. Ainsi, nous sommes passés en l'espace de 30 ans d'un processeur élémentaire composé de quelques milliers de transistors à des processeurs très complexes composés de plusieurs centaines de millions de transistors. Les progrès continuels ont permis de produire des circuits de plus en plus performants et de réaliser des systèmes électroniques complexes nécessaires dans un grand nombre d'applications quotidiennes. La figure I.1 [1] donne une idée sur le progrès en microélectronique.

Figure I-1 : représentation de l'évolution du niveau d'intégration des circuits intégrés selon la loi de Moore.

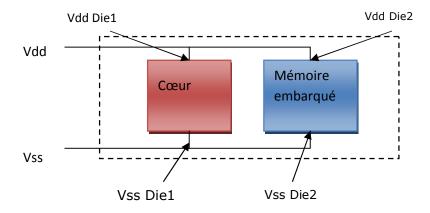

Cette évolution ne s'est pas faite sans difficultés, en effet le nombre d'entrées sorties (E/S) et donc d'interconnexions entre circuits a augmenté, causant une dégradation de la qualité des signaux et une réduction de la bande passante des interfaces digitales rapides. Pour faire face à ces problèmes, la solution proposée vise à réduire les longueurs des interconnexions entre circuits en les rapprochant. Pour cela, deux types d'intégration ont été proposés :

\_ L'intégration sur puce ou System on Chip (SoC), qui vise à réaliser sur le même substrat de plus en plus de fonctions électroniques. Il s'agit d'une conséquence de la miniaturisation suivant la loi de Moore.

\_ L'intégration package ou System in Package (SiP), qui vise à assembler dans le même boîtier plusieurs circuits. La miniaturisation concerne tout le système, à la fois les composants discrets mais aussi la carte, qui se retrouve aussi dans le boîtier.

Cela permet d'atteindre un taux de réduction plus grand que celui prévu par loi de Moore.

En combinant l'évolution de l'intégration sur puce avec celle de l'intégration package, la miniaturisation des composants électroniques suivrait une tendance plus rapide que la loi de Moore, qu'on appelle « more than Moore ». Ces deux approches ont leurs avantages et leurs inconvénients. Cependant, dans les deux cas, les composants se comportent comme des sources et victimes de perturbations électromagnétiques. [1]

#### b) Historique de la circuiterie logique

Les premiers circuits logiques furent des circuits asynchrones à relais (l'additionneur Model K de G.R. Stibitz en 1937). Cette technologie issue de la téléphonie se développa entre les années 1930 et 1950. Des montages à tube à vide furent aussi utilisés pour le traitement en temps réel des images Radar dans les années 1940 et 1950. La différence importante de tension entre l'entrée (la grille) et la sortie (l'anode) des tubes à vide compliquait beaucoup la réalisation de couplages directs entre les étages successifs.

Cela conduisit à utiliser des couplages capacitifs et une représentation des grandeurs logiques sous la forme d'impulsions qui véhiculaient simultanément les valeurs. Les montages électroniques de cette époque se comportaient comme un réseau de fonctions parcourues par des impulsions d'activation.

La grande nouveauté des ordinateurs s'est située dans la réutilisation d'un petit ensemble de fonctions pour effectuer une grande variété de tâches. Les ordinateurs conçus au début des années 1960 étaient asynchrones et continuaient à utiliser la logique à impulsions, malgré le fait que l'utilisation de transistors permet de réaliser des couplages directs (comme par exemple dans la circuiterie RTL (pour Resistor-Transistor Logic).

Les durées allouées aux opérateurs pour fonctionner étaient déterminées par des batteries de monostables dont le réglage nécessitait un doigté certain. Pour « assainir » le fonctionnement

de ces machines, la logique synchrone à niveau fut utilisée à partir du milieu des années 1960. Elle déboucha sur la création de grandes familles logiques comme la TTL qui perdure encore jusqu'à maintenant après son passage en CMOS. [17]

L'arrivée des circuits VLSI « complexes » dans les années 1970 posa un nouveau problème. Leur technologie, complètement nouvelle, n'était pas réalisée avec une grande précision et des variations importantes de leurs caractéristiques étaient fréquentes entre les lots de circuits. Pour s'affranchir de ce problème, une logique polyphasée, basée sur le principe des écluses, fut utilisée. De plus, comme le nombre de transistors disponibles était toujours inférieur aux désirs des concepteurs, ceux-ci inventèrent des astuces pour en utiliser le moins possible. La logique dynamique et celle d'interrupteurs firent leur entrée (ou plutôt leur retour !). Pendant ce temps, la logique monophasée était devenue le classique des électroniciens qui l'utilisaient pour réaliser des cartes. L'augmentation constante de la complexité des circuits intégrés laissait prévoir la limite de la logique synchrone dès 1980. Deux familles de solutions furent proposées :

- La logique asynchrone « moderne » fut proposée dès 1980 sous la forme de l'utilisation de signaux impulsionnels transmis de manière différentielle par un protocole de poignée de main.

Après plus de 25 ans d'efforts, cette proposition académique reste un sujet d'avenir. [17]

- Des techniques de synchronisation des circuits très complexes furent mises au point dans les années 1990 et conduisirent au développement des microprocesseurs modernes. Ces circuits sont constitués de blocs synchrones qui reçoivent une horloge centrale localement resynchronisée. Les contraintes de test dues à la complexité des circuits et aux risques de parasitage entre les lignes métalliques, associé au fait que le nombre de transistors n'est plus une contrainte, conduisirent à l'abandon de la logique polyphasée ainsi que des techniques de logique dynamique et d'interrupteurs qui posaient des problèmes de test, mais surtout qui n'entraient pas dans la culture classique des électroniciens malgré les avantages importants qu'elles auraient pu apporter. L'avenir de l'électronique est la réalisation de petits appareils très complexes, mais portables et de grande autonomie. [17]

#### c) Composition døun circuit intégré

De manière simple, un circuit intégré digital ne comprend que des structures de calcul et des structures d'interface par lesquelles les résultats ou les requêtes sont échangés avec l'environnement extérieur. Tous les circuits intégrés remplissent ces fonctions à des degrés divers : les microprocesseurs traitent majoritairement des instructions logicielles, les DSP (Digital Signal Processor) traitent davantage les signaux par des calculs complexes et les microcontrôleurs sont quant à eux dédiés à la gestion et à la coordination d'autres circuits intégrés, ce qui implique le traitement d'instructions et de protocoles ainsi qu'un grand nombre d'interfaces de communication. La polyvalence des microcontrôleurs en fait des circuits employés dans de grands nombres d'applications. Leur architecture répond donc à ce besoin. [17] [18]

-La puce dont les rails d'alimentation ainsi que toutes les entrées sorties sont reliées à des pads, est composée de plusieurs éléments qui réalisent la fonction à laquelle est dédié le circuit, nous trouvons ainsi :

Cœur : L'architecture est organisée autour de l'unité de calcul et de traitement de données, que l'on nomme cœur du composant ou CPU (Central Processing Unit). Ce cœur comporte une Unité Arithmétique et Logique (ALU) où sont effectués les calculs. On y trouve aussi des registres de configuration, qui stockent les états du système à un instant donné, et des piles où l'on place et ordonne les instructions à exécuter.

Bus interne : Le cœur est relié par des bus de données ou de communication aux blocs dédiés à des fonctions spécifiques ou à des interfaces. La fréquence de ce bus est un des critères de rapidité d'exécution du composant. La taille d'adressage de ce bus permet de classer le microcontrôleur : nous trouvons ainsi des bus de 4, 8, 16, 32 voire 64 bits.

Mémoire : Le premier de ces blocs est la zone de mémoire, qui contient de la mémoire vive (RAM : Random Access Memory), utilisée pour stocker les données temporaires de calcul ou de transfert, et de la mémoire morte (ROM : Read Only Memory) qui sert à conserver des programmes et données de manière permanente une fois l'alimentation coupée. Les temps nécessaires pour lire ou écrire en mémoire RAM seront bien inférieurs à ceux de la mémoire ROM.

Autres blocs : nous citerons des convertisseurs ADC (Convertisseur Analogue Digital), des interfaces de communication spécifiques (SPI, SCI, I2C, ...), des ports d'interface génériques des (données)...[18]

-Un bonding reliant les pads de la puce aux pattes (les leads) du boitier par l'intermédiaire de fils d'or qui peuvent atteindre quelque cm dans le cas des boitiers de type PGA (Pin Grid Array).

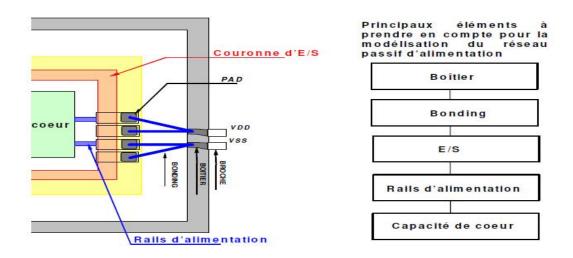

Figure I-2 : représentation des différentes parties constituant un circuit intégré

-Le boitier : il est en quelque sorte la capsule du circuit, ces broches (ou billes pour les boitiers BGA) sont reliées au pads par des accès dont les longueurs sont également importante (même ordre que le bonding).La figure I-2 [18] rend compte de l'agencement de ces différents composants.

Lorsque la fréquence de fonctionnement du circuit augmente, ces composants deviennent des sources de perturbations non négligeables, qui affectent grandement la compatibilité du circuit avec les composants environnants.

#### II) Définitions préliminaires relatives à la compatibilité électromagnétique

#### a) La compatibilité électromagnétique

La CEM (Compatibilité ElctroMagnetique) est « l'aptitude d'un dispositif, d'un appareil ou d'un système à fonctionner dans son environnement électromagnétique de façon satisfaisante et sans produire lui-même des perturbations électromagnétiques intolérables pour tout ce qui se trouve dans cet environnement ». [6]

#### b) La perturbation électromagnétique

Les perturbations électromagnétiques englobent tous les signaux indésirables, involontaires susceptibles de nuire au fonctionnement des circuits et autres équipements électroniques. Une perturbation électromagnétique peut être soit rayonnée soit conduite, on parlera donc de couplage en mode rayonné ou conduit respectivement.

- Couplage en mode rayonné : c'est un couplage qui se fait par induction d'un courant électrique par une onde électromagnétique sur les interconnections ainsi que sur le boitier du circuit intégré.

- Couplage en mode conduit : c'est un couplage pour lequel les lignes d'alimentation ou de masse des cœurs digitaux ou des entrées/sortie sont les principaux vecteurs de propagation, Il faut donc disposer, au préalable, d'un schéma équivalent faisant apparaître tous les composants, même ceux qui ne sont pas intentionnellement destinés à faire partie du circuit (les composants modélisant des parasites). [19]

#### c) La susceptibilité et lømmunité des circuits intégrés

La susceptibilité d'un circuit intégré représente sa sensibilité ou le degré de fragilisation de son fonctionnement correct par différents types d'émissions extérieures. Il s'agit de fixer un seuil de contrainte sous lequel le circuit est dit immunisé contre les perturbations.

L'immunité est donc l'aptitude d'un équipement à ne pas être perturbé lorsqu'il est soumis à une perturbation électromagnétique d'amplitude définie. Les émissions génératrices de perturbation électromagnétique ont des origines variées. [19]

#### III) Sources de perturbations extérieures

Les circuits intégrés sont certes une source de perturbation comme remarqué mais malheureusement elle n'est pas la seule, en effet il existe de nombreuses sources de perturbation électromagnétique (figure I-3 [1]) dont certaines d'origine naturelles et qui ne seront pas citées dans ce travail. La liste de ces sources n'est pas exhaustive car leur nombre tend à augmenter avec l'évolution technologique. [1]

Figure I-3 : Exemple de sources de perturbation électromagnétique

#### IV) Origines des émissions parasites des circuits intégrés

#### a) Bruit de commutation simultanée(SSN)

Les émissions électromagnétiques des systèmes électroniques trouvent leur origine au cœur des circuits intégrés. Ce phénomène provient du bruit de commutation simultanée SSN (Simultaneous Switching Noise) généré par les appels de courant dûs à la commutation des différentes portes logiques du circuit.

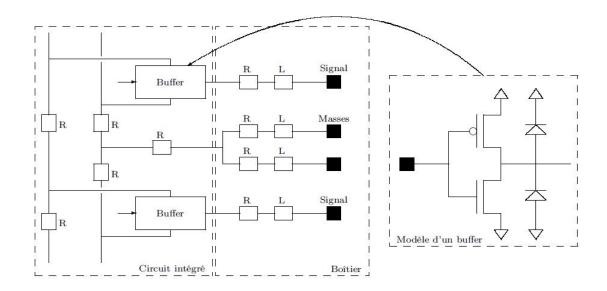

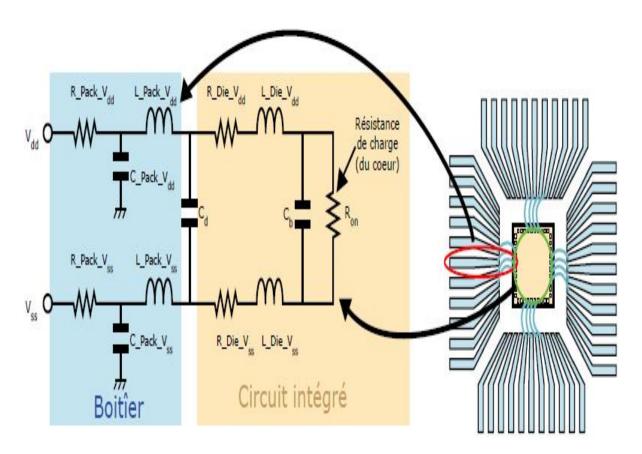

Les alimentations et les références de masse parviennent aux circuits par l'intermédiaire d'un ensemble d'interconnexions, formées par les broches des boîtiers et le réseau d'alimentation interne. Toutes ces lignes représentent autant d'inductances et de résistances parasites qui, dès

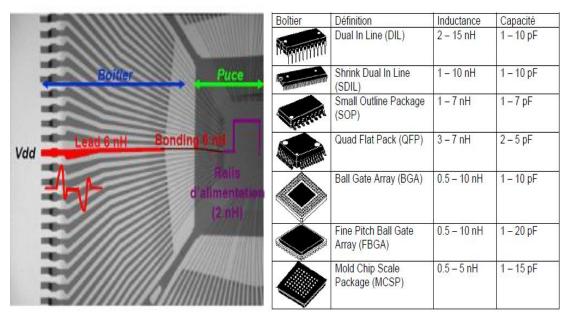

qu'elles sont traversées par un courant variable, induisent une variation de potentiel. Le boîtier représente le contributeur majeur à l'inductance parasite, tandis que le réseau d'alimentation interne est plus résistif. La figure I-4 [1] décrit l'ensemble des inductances et des résistances parasites à l'intérieur d'un circuit intégré qui sont responsables de l'apparition du SSN, avec les valeurs des éléments parasites introduits par différents types de boîtiers couramment utilisés.

Figure I-4 : Inductances parasites liées aux interconnexions d'un circuit intégré (à gauche) et caractéristiques électriques des différents types de boitiers (à droite).

Le bruit lié au passage du courant de commutation des circuits au travers des inductances parasites des différentes interconnexions est appelé  $\Delta I$  noise dont l'amplitude peut être évaluée à partir de l'équation suivante [18] [1] :

$$V_{\Delta I \ noise} \approx L \times \frac{di}{dt}$$

(Équation I-1) [1]

Avec : L : Inductance parasite du chemin d'alimentation.

di/dt: Pente du courant traversant les interconnexions.

Néanmoins, le chemin d'alimentation est aussi constitué d'une petite résistance parasite, variant de  $100 \text{ m}\Omega$  à  $10 \Omega$  suivant la technologie et la taille du circuit. Le bruit lié au passage du courant appelé lors de la commutation des circuits au travers des résistances parasites est appelé IR noise. Avec l'augmentation de la résistance des interconnexions à chaque nœud, l courant IR noise devient un problème de plus en plus contraignant.

Alors que le  $\Delta I$  noise entraîne une fluctuation de tension, le IR noise entraîne une chute de potentiel et dégrade les vitesses de commutation des portes logiques, faisant ainsi apparaître des délais parasites. Cependant, l'ajout de résistances sur les rails d'alimentation permet d'amortir les oscillations produites par le  $\Delta I$  noise et de réduire le bruit de commutation. Ainsi, la cumulation de ces deux effets permet de calculer l'amplitude du bruit de commutation. [1]

$$V_{SSN} = R \times i + L \times \frac{di}{dt}$$

(Équation I-2) [1]

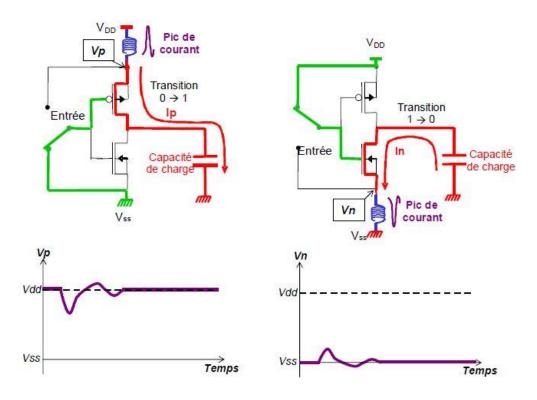

La figure I-5 [8] décrit le phénomène de génération de bruit de commutation simultanée et la variation de tension d'alimentation produite.

Figure I-5 : Courant circulant dans un inverseur CMOS lors de sa commutation et génération de bruit de commutation simultanée sur les lignes d'alimentation.

L'amplitude du bruit de commutation dépend d'un certain nombre de facteurs sur lesquels sont basés de nombreux modèles pour sa prédiction, elle dépend de :

- La forme de l'appel de courant

- Les paramètres technologiques et géométriques des transistors

- Le nombre de portes commutant simultanément

- L'impédance du chemin d'alimentation ou de masse

- La disposition des plans d'alimentation et de masse

- La capacité de charge

Le tableau I-1 [1] présente les appels de courant typiques en fonction des technologies. Il apparaît clairement que l'amplitude du pic de courant et donc le bruit de commutation simultanée augmentent avec l'évolution technologique. On peut remarquer que, même si le pic de courant généré par porte ainsi que la tension d'alimentation diminuent, l'appel de courant total augmente puisque les circuits deviennent de plus en plus denses.

| Technologie | Tension<br>d'alimentation<br>(V) | Densité de<br>portes<br>(/mm²) | Pic de courant (mA/porte) | Capacité<br>(fF/porte) | Pic de courant (A/mm²) |

|-------------|----------------------------------|--------------------------------|---------------------------|------------------------|------------------------|

| 1.2 µm      | 5                                | 8K                             | 1.1                       | 60                     | 8.8                    |

| 0.8 μm      | 5                                | 15 K                           | 0.9                       | 40                     | 13.5                   |

| 0.5 μm      | 5                                | 28 K                           | 0.75                      | 30                     | 21                     |

| 0.35 μm     | 5 – 3.3                          | 50 K                           | 0.6                       | 25                     | 30                     |

| 0.25 μm     | 5 – 2.5                          | 90 K                           | 0.4                       | 20                     | 36                     |

| 0.18 μm     | 3.3 – 2                          | 160 K                          | 0.3                       | 15                     | 48                     |

| 0.12 μm     | 2.5 – 1.2                        | 240 K                          | 0.2                       | 10                     | 48                     |

| 90 nm       | 2.5 – 1                          | 480 K                          | 0.1                       | 7                      | 48                     |

| 65 nm       | 2.5 – 0.8                        | 1000 K                         | 0.07                      | 5                      | 50                     |

| 45 nm       | 1.8 – 0.8                        | 2000 K                         | 0.05                      | 3                      | 55                     |

Tableau I-1 : évolution des pics des courants en technologie CMOS.

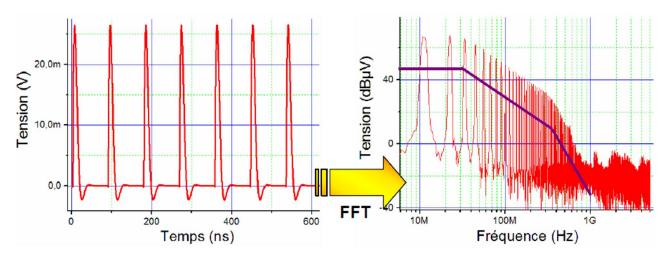

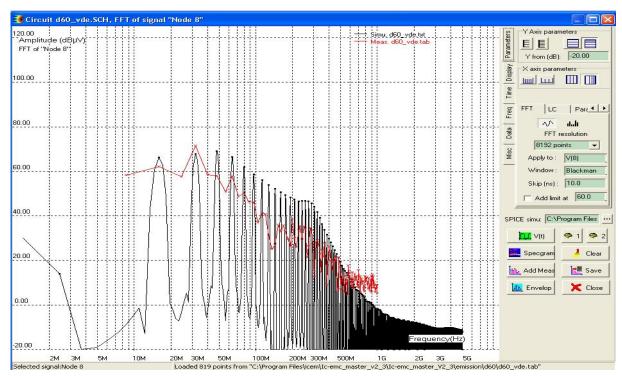

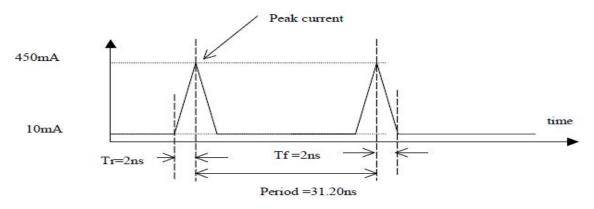

La figure I-6 [1] présente un exemple de bruit de commutation simultanée ainsi que sa transformée de Fourier. La forme de cet appel de courant peut être représentée en première approximation par un triangle. Ce bruit est caractérisé par des temps de montée et de descente rapides lui conférant de nombreuses composantes harmoniques à haute fréquence. L'analyse de son spectre montre qu'il couvre quasiment deux décades du spectre radiofréquence.

Figure I-6 : exemple de bruit de commutation simultanée et son spectre de fréquence.

Fort heureusement, des solutions ont été proposées pour réduire le SSN. Certaines sont empiriques tandis que d'autres proviennent d'analyses tirées des mesures et des simulations. Voici une liste non exhaustive des solutions existantes :

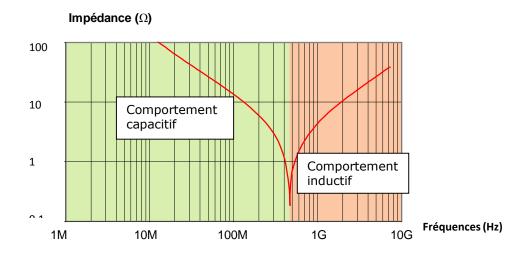

D'abord, pour réduire le SSN, il faut contrôler l'impédance des chemins d'alimentation, en réduisant les inductances parasites grâce à l'utilisation d'alimentations adaptées, d'assignation d'E/S ou l'utilisation de boîtiers faible inductance. L'impédance des chemins d'alimentation peut aussi être contrôlée en ajoutant des capacités de découplage. Plus celles-ci se trouvent à proximité de la source d'émission, plus elles sont efficaces, ce qui conduit à ajouter des capacités non seulement sur la carte ou Printed Circuit Board (PCB), mais aussi à l'intérieur des boîtiers et directement sur le silicium (capacité on-chip).

D'autres techniques consistent à isoler les blocs bruyants des blocs sensibles. Cela consiste principalement à séparer les alimentations des blocs de nature diverse et à isoler les blocs sur le silicium en créant des caissons d'isolation et des anneaux de garde.

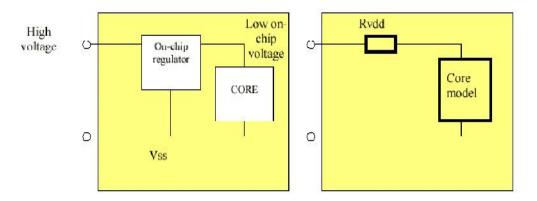

Enfin, on peut aussi directement agir sur la source d'émission. Par exemple, en contrôlant l'appel de courant en étalant, dans le temps, la consommation en courant. Par exemple en ajoutant de la désynchronisation aléatoire ou jitter sur les signaux d'horloge ou en contrôlant le temps de commutation ou slew rate des E/S, sont très efficaces pour diminuer l'amplitude du pic de courant. D'autres stratégies plus récentes consistent à venir réduire localement les variations de tension en implantant des régulateurs de tension intégrés au plus près des blocs bruyants. [1]

#### b) Sources démissions dans un circuit intégré

Les circuits qui se caractérisent par des commutations nombreuses et simultanées, et en général, qui connaissent des variations de courants trop brusques et les appels de courant les plus importants, sont les plus bruyants. Certains blocs dans un circuit intégré sont plus bruyants que d'autres, et entre autre, les blocs les plus perturbateurs et qui sont donc assimilés aux sources des émissions parasites sont :

Les blocs digitaux synchrones qui créent un appel de courant à chaque front de l'horloge de synchronisation. Le bruit est causé principalement par l'activité des cœurs numériques qui augmente à chaque nouvelle génération de circuit.

Les entrées/sorties : Le bruit produit par la commutation des entrées/sorties est très important puisque celles-ci sont constituées de transistors MOS capables de fournir un courant important. Leurs états logiques dépendent des données qu'elles transportent à l'intérieur ou à l'extérieur du circuit intégré. Plus le nombre d'entrées/sorties commutant en même temps augmente et plus elles sont rapides, plus le bruit généré augmente.

Les arbres d'horloge, qui distribuent le signal d'horloge et propagent le bruit à l'ensemble du circuit.

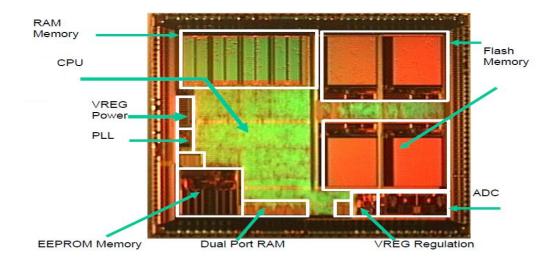

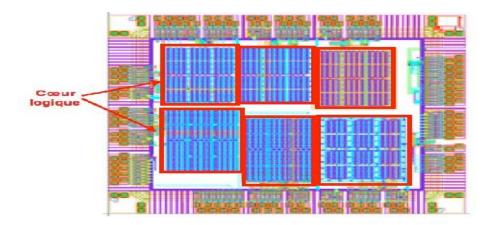

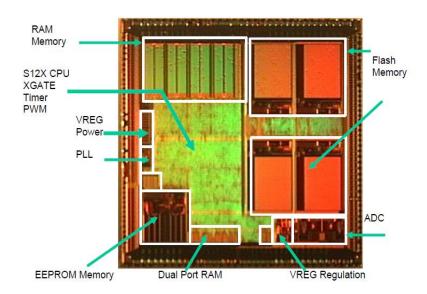

Certains blocs analogiques tels que des amplificateurs de puissance ou des PLL, qui peuvent produire des émissions parasites concentrées sur quelques harmoniques. Ces différents blocs peuvent être intégrés à l'intérieur du même circuit, comme dans un microcontrôleur qui intègre des blocs digitaux, des entrées/sorties, des convertisseurs analogique numérique (ADC Analog Digital Converter), des PLL et des blocs analogiques. La figure I-7 [1] présente une vue du placement des différents blocs ou floorplan d'un microcontrôleur. 16 bits.

Figure I-7 : le floorplan (disposition des blocs) d'un microcontrôleur 16 bits.

#### V) Propagation du bruit émis

#### a) Mécanismes de propagation conduite

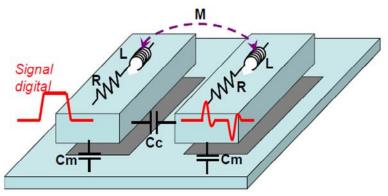

Le bruit se propage principalement à l'intérieur des circuits ou sur les PCB par couplage conduit. Les lignes d'alimentation ou de masse des cœurs digitaux ou des entrées sortie sont les principaux vecteurs de propagation, puisque la commutation des cœurs numériques ou des entrées sorties génère des fluctuations de tension sur les alimentations. Une modélisation complète des résistances et des inductances parasites des interconnexions permet de déterminer l'amplitude du bruit conduit. La propagation peut se faire aussi par couplage entre interconnexions voisines. Ce couplage, appelé aussi diaphonie ou crosstalk, peut être soit de nature inductive, soit de nature capacitive. La figure I-8 décrit le phénomène.

Figure I-8: Couplage en mode conduit inductif et capacitif entre deux interconnexions.

A l'intérieur des circuits intégrés, puisque les interconnexions sont très peu inductives et très rapprochées, le couplage est capacitif, contrairement aux boîtiers où le couplage est plutôt de nature inductive. Celui-ci joue un rôle prépondérant dans la génération de couplages diaphoniques et peut être responsable de fluctuations de niveaux de tension internes. Le couplage entre interconnexions prend une importance cruciale dès que les fréquences des signaux des entrées/sorties augmentent. En effet, l'amplitude de tensions induites par la diaphonie dépend du temps de montée des signaux. De plus, plus les signaux sont rapides, plus ils sont sensibles à toute forme de dégradation.

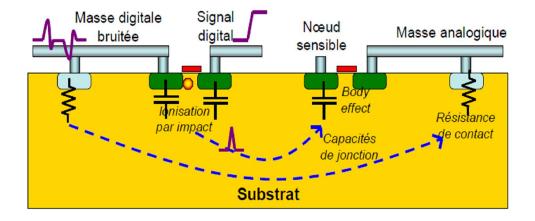

A l'intérieur des circuits, un autre couplage est aussi à l'œuvre. L'ensemble des blocs d'un même circuit partage le même substrat. Du fait de son faible dopage, celui-ci présente une résistivité élevée offrant une bonne isolation entre les différents blocs. Cependant, les blocs bruyants tels que les blocs digitaux peuvent injecter du bruit dans le substrat, qui va se propager vers des blocs sensibles tels que les blocs analogiques et éventuellement les perturber. Ce phénomène appelé couplage substrat est un des principaux freins au développement de l'intégration de systèmes sur puce (SoC ou System on Chip) mixant des blocs analogiques et numériques. Différents mécanismes d'injection sont détaillés sur la figure I-9 [19]:

Par les contacts de polarisation du substrat ; si une alimentation bruitée vient polariser le substrat, alors le bruit est directement injecté dans le substrat à travers la résistance formée par le contact.

Le couplage capacitif entre le substrat et les différents éléments d'un circuit, tels que les jonctions PN au niveau des drains et des sources, les interconnexions des niveaux de métaux inférieurs, et les caissons d'isolation. Ce mode est particulièrement important pour les blocs digitaux rapides.

Le courant d'ionisation par impact, dû à la création de porteurs chauds formés entre le drain et la source des transistors mis en saturation et qui sont injectés dans le substrat. Ce phénomène est prépondérant jusqu'à quelques dizaines de mégahertz et prend de l'importance avec la réduction de la taille des circuits.

Figure 1.0 . Magazine and design at the state of the stat

#### b) Mécanismes de couplage rayonné :

Toute interconnexion peut jouer le rôle d'antenne, de manière plus ou moins efficace à une fréquence donnée. Ainsi, dès que la longueur L d'une interconnexion s'approche de  $L \approx \frac{\lambda}{4}$  celle-ci joue un rôle d'antenne et les courants qui la traversent ou la tension à ses bornes peuvent engendrer un champ électromagnétique. Le tableau I-2 [1] donne une idée des structures pouvant jouer le rôle d'antenne en fonction de la fréquence.

| Fréquence         | 10 MHz     | 100 MHz | 1 GHz     | 10GHz        |

|-------------------|------------|---------|-----------|--------------|

| Longueur d'onde λ | 30 m       | 3 m     | 30 cm     | 3 cm         |

| λ/4               | 7.5 m      | 75 cm   | 7.5 cm    | 7.5 mm       |

| Antenne physique  | Long câble | Câble   | Piste PCB | Lead boîtier |

Tableau I-2 : Dimension d'antenne en fonction de la fréquence et identification des parties susceptibles de jouer ce rôle.

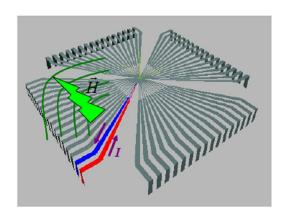

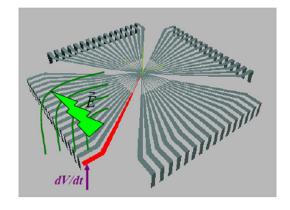

La circulation d'un courant à l'intérieur d'une boucle (formée par exemple par un conducteur et son retour à la masse) constitue une source efficace de champ magnétique, alors que la variation de potentiel d'une interconnexion (par exemple la commutation d'une broche d'un port de microcontrôleur) constitue une source efficace de champ électrique. La figure I-10 [1] illustre les mécanismes de génération des champs électrique et magnétique à proximité des broches d'un boîtier.

Figure I-10 : Mécanismes de génération des champs magnétique (à gauche) et champ électrique (à droite)

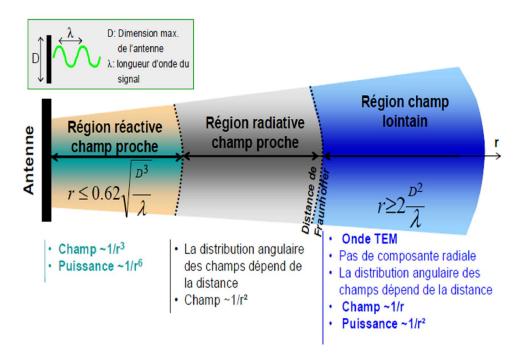

Le rayonnement produit par n'importe quelle antenne peut se séparer en trois zones, décrites sur la figure I-11. [1]

Nous distinguons les zones suivantes :

La zone de rayonnement en champ proche, qui se situe à proximité de l'antenne. A l'intérieur de cette zone, l'onde plane ne s'est pas encore formée et la distribution des composantes du champ dépend de la distance à l'antenne. L'amplitude des composantes du champ se met à décroître très rapidement à mesure qu'on s'éloigne de l'antenne.

La zone de Fresnel, qui est une zone intermédiaire.

La zone de champ lointain, où l'onde plane est localement formée. Celle-ci est qualifiée d'onde transverse électromagnétique ou TEM.

Figure I-11 : Régions électromagnétiques d'une antenne.

#### VI) Couplage des perturbations externes

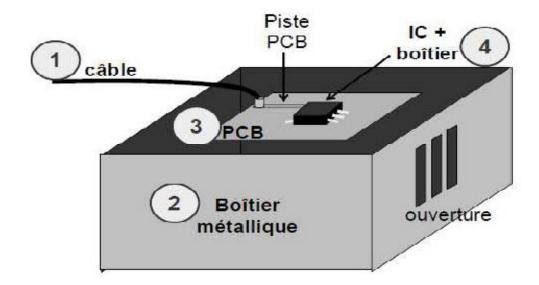

Avant de perturber un circuit, la perturbation doit se coupler à celui-ci, soit de manière rayonnée, soit de manière conduite. Nous n'allons considérer ici que le bruit provenant d'une source extérieure. Tout l'environnement du circuit intégré peut coupler une partie de l'énergie d'une perturbation incidente par effet d'antenne et ainsi influencé la susceptibilité du système électronique. En effet, les structures de couplage vont être à l'origine de résonances dont les fréquences sont liées à leurs dimensions. En outre, chacune de ces structures est constituée d'éléments électriques parasites qui vont modifier la pénétration de l'onde à l'intérieur du

circuit en fonction de la fréquence. Nous allons décrire les différents niveaux du système électronique décrit par la figure I-12 [1] et leurs influences sur la susceptibilité

Figure I-12 : Les différents niveaux d'un système électronique.

Le mode de couplage principale sont les câbles, en effet ils sont considérés comme des antennes à des fréquences en dessous de 1 GHz qui permettent en suite aux perturbations de se propager de manière conduite aux déférents circuits composants le système. On trouve ensuite à une échelle moindre le PCB (circuit imprimé), en effet les pistes de ces derniers forment des antennes à partir de quelque centaines de MHz et sont considérées comme des lignes de transmission miniature.

On peut aussi citer l'influence de structures telles que des radiateurs placés sur le capot des circuits dans le couplage du champ électrique incident. En effet, un radiateur peut former avec le plan de masse du PCB une cavité électromagnétique ou une antenne, qui couplera de manière efficace le champ incident.

Le boitier est une partie inévitable du chemin de couplage, c'est le dernier étage avant le circuit même s'il constitue une antenne moins efficace que les câbles et les pistes du PCB. En effet les broches du circuit intégré représentent des résistances et des inductances parasites qui présentent des bandes passantes limitées dont les fréquences de coupures varient selon le type de boitier. [1]

#### VII) Effets des perturbations sur le comportement des circuits intégrés

Après avoir abordé la génération, la propagation et les modes de couplage d'un champ électromagnétique, nous allons nous intéresser aux effets que les perturbations peuvent avoir sur les systèmes électroniques. Pour cela, nous distinguerons les composants analogiques des composants numériques puisque leurs réactions sont sensiblement différentes.

#### a) Composants analogiques

Selon la fréquence deux cas peuvent se présentés pour une perturbation électromagnétique dans le premier la fréquence de la perturbation est en dehors du domaine de fonctionnement normale du circuit intégré, dans le second cas elle est incluse dans ce domaine.

#### 1) Hors-bande de fréquence du composant

Vu la caractéristique intrinsèque inhérente aux circuits intégrés en général et aux circuits analogiques plus particulièrement qui se comportent comme des filtres passes bas, pour qu'une perturbation dans le domaine de fréquence de fonctionnement du composant puisse générer le même dysfonctionnement hors bande, il lui faudrait une énergie plus élevé.

#### 2) Dans la bande de fréquence du composant

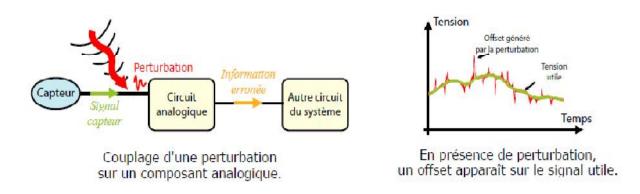

Une perturbation caractérisée par une faible variation de tension ou de courant perturbera de manière sensible le fonctionnement d'un capteur de pression, de température et tout autre composant analogique. La perturbation va se superposer au signal utile créant de fait une tension d'offset, cette tension sera analysée avec le signal utile par le système de contrôle qui traitera donc des données erronées avec toutes les erreurs qui en découlent. La figure I-13 [19] montre le principe de couplage d'une perturbation à un circuit analogique ainsi que la tension d'offset qui en découle.

Figure I-13 : Couplage (à gauche) et génération d'offset (à droite) due à une perturbation électromagnétique sur un composant analogique.

D'autre effet peuvent exister, nous pouvons ainsi souligner une baisse de résolution, un gain plus faible, une baisse du rapport signal sur bruit, la distorsion des signaux et la fluctuation de la tension d'alimentation. En effet bon nombres de composants analogique tel que les convertisseurs analogique/numérique ou numérique/analogique y sont particulièrement sensible. La sensibilité des convertisseurs est due au fait que l'alimentation leur sert également de référence, par rapport à laquelle les données délivrées sont prises. De surcroît, plus la résolution porte sur un nombre important de bits, et plus la susceptibilité du composant est forte. Les perturbations induites sur les amplificateurs sont en général due à des

fluctuations de leur alimentation car ces derniers tirent leur puissance de l'alimentation, des fluctuations des niveaux d'amplification sont des lors perceptibles d'autant plus s'il s'agit d'amplificateurs audio, ainsi l'étage différentiel des amplificateurs est un élément critique qui conduit les modes commun et différentiel.

Il est à noter que les bruits induits sur des composants analogiques sont la plus part du temps temporaires et disparaissent avec la disparition de la perturbation, malheureusement on ne peut pas dire autant des composants numériques.[19]

#### b) Circuits numériques

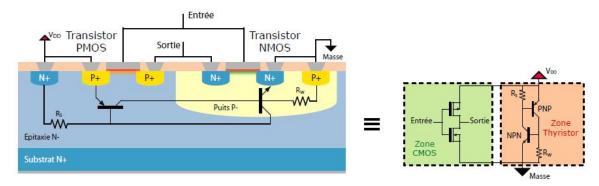

#### 1) Phénomène de latchup

Le phénomène de latchup est dû à la mise en conduction involontaire (suite à une perturbation électromagnétique par exemple), d'une succession de jonctions PNPN formant un thyristor parasite entre l'alimentation et la masse (Figure I- 14 [1]). Le déclenchement du thyristor parasite provoque un court-circuit entre l'alimentation et la masse du circuit intégré qui peut être destructif. [8] [19]

Figure I-14 : Phénomène du latchup dans les circuits intégrés numériques

#### 2) Effet sur les sorties

Un autre élément des composants numériques peut s'avérer susceptible : la sortie d'un composant élémentaire. Du fait de sa faible impédance, une sortie numérique peut être perturbée par l'injection d'un courant parasite d'amplitude relativement faible (de l'ordre de la dizaine de milliampère). L'effet d'une telle perturbation se traduit généralement par un changement d'état de la sortie.

#### 3) Effet sur les entrées

Bien que leur impédance soit relativement élevée en comparaison de celles des sorties, les entrées numériques peuvent également être perturbées. En effet, la réduction des tensions d'alimentation s'accompagne d'une réduction des seuils de commutation et par conséquent d'une diminution des marges de bruits en entrée. De ce fait, les entrées sont toutes aussi susceptibles. Et cette susceptibilité se traduit, comme pour les sorties, par une inversion du niveau de l'information d'entrée.

#### 4) Changement détat des bascules et mémoires

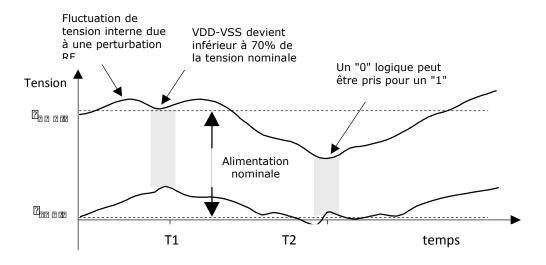

L'augmentation ou la diminution des tensions grille source des transistors due a une perturbation sur les alimentations crée une variation de courant causant de fait une modification du temps de transition (erreur de délai). Les perturbations des alimentations transmises sur les sorties des portes logiques peuvent induire un changement d'état suivant que la perturbation est supérieure au seuil de commutation ou pas (changement d'état logique).

Une conséquence des deux effets précédents peut être la mémorisation d'un niveau logique erroné dans une bascule ou une mémoire. En effet, les variations de délais peuvent provoquer des erreurs de temps d'arrivée et de maintien des données en entrée des bascules. De plus, une commutation erronée de l'horloge ou d'un signal peut également entraîner des erreurs de mémoires. Il est bien évident que de telles erreurs pourraient mettre à mal le fonctionnement d'un système. [19]

#### Conclusion

Ce chapitre est un résumé non exhaustif sur la compatibilité électromagnétique des circuits intégrés, nous y avons vu notamment certaines des problèmes qu'on peut rencontrer dans ce domaine ainsi que les différents modes de propagation des perturbations électromagnétiques et leurs influences sur le fonctionnement des circuits intégrés.

Les technologies à base de circuits intégrés sont partout, de la voiture à l'avion en passant par les satellites, elles sont de nos jours inévitables dans bien des applications dont l'utilité n'est plus à prouver, augmentant les risques de disfonctionnement due à une éventuelle sensibilité des circuits aux agressions. Aussi la garantie du bon fonctionnement de ces équipements représente un gage de professionnalisme des fondeurs (fabriquant de circuits intégrés). En effet c'est dans le but de réduire les coûts de fabrication, de mettre sur le marché des circuits fiables que les différents fabricants de circuits intégrés ont mis aux points différents méthodes d'analyse et de simulation dans le domaine des circuits intégrés. Les deux chapitres suivants vont traiter des modèles sur lesquels se base la simulation des problèmes de CEM, dans ces deux volets à savoir la modélisation et la simulation des émissions parasites et de la susceptibilité des circuits intégrés.

# **Chapitre II:**

Modèles démission des circuits intégrés

#### Introduction

Ces dernières années les clients des fabricants de circuits intégrés imposent de plus en plus de contraintes du point de vue CEM, celle-ci doit être prise en compte le plus tôt possible dans les phases de fabrication. En effet, dans les années 90, la validation CEM d'un circuit ne se faisait qu'après fabrication et par mesure. Afin d'éviter des phases de rectifications, coûteuses en temps et en argent, la prédiction des niveaux de bruit généré par les circuits intégrés doit être mise en place au cours des étapes de conception, rendant nécessaire le développement de modèles de prédiction. Actuellement, les fabricants disposent d'outils et de flots de simulation permettant de prédire l'amplitude du SSN à partir d'informations telles que le « floorplan » et des « netlists » au niveau transistor, afin d'estimer les appels de courant et les parasites introduits par les interconnexions. Ainsi, il est possible de vérifier lors des phases de fabrication si les circuits respectent les marges de bruit requises.

Cependant, l'émission électromagnétique ne concerne pas seulement les circuits intégrés, mais aussi le système complet qui peut englober plusieurs circuits. Comme nous l'avons vu précédemment, des domaines comme l'automobile et l'aéronautique sont soumis à des contraintes très strictes au point de vue CEM et donc à la même problématique de prédiction du niveau d'émission durant les étapes de design. Pour prendre en compte l'émission des circuits intégrés dans l'émission globale du système et tester l'effet de techniques de réduction du bruit, les équipementiers exigent des fondeurs des modèles d'émission conduite et rayonnée de leurs composants. Cela pose plusieurs contraintes au niveau des modèles que doivent fournir les fondeurs :

- -Non confidentialité des modèles, interdisant l'emploi de modèles au niveau transistor, de schématiques complètes des circuits

- -Rapidité de simulation, ce qui oblige à réduire la complexité des modèles

- -Compatibilité avec des outils standards tels que SPICE et VHDL-AMS

Le but de ce chapitre est d'étudier les modèles de prédiction de l'émission des circuits intégrés, notamment ceux sur les quelles se base la simulation des problèmes de compatibilité électromagnétique qu'effectue le logiciel IC-EMC.

# I) Aperçu sur les méthodes de mesure de løémission des circuits intégrés en mode rayonné

La réduction des dimensions des circuits intégrés et leur montée en fréquence s'est accompagné d'un certain nombre de problèmes. En effet leur activité interne engendre des émissions électromagnétiques qui peuvent être néfastes pour les circuits et autre composant environnants. Ainsi dans les réseaux de systèmes électroniques, les circuits intégrés et les circuits imprimés, l'énergie électrique et magnétique peuvent se représentées sous trois formes différentes :

- -Une forme conduite dans la quelle le courant se propage à travers les fils et les lignes pour atteindre les composants.

- -Une forme rayonnée en champ proche dans la quelle l'énergie est emmagasinée dans des capacités et des inductances.

- -Une forme rayonnée en champ lointain dans laquelle l'énergie est rayonnée sous forme d'ondes électromagnétiques.

- -Une source de bruit peut être incluse dans n'importe laquelle de ces formes néanmoins elles sont toutes décrites par le théorème du Poynting.

Ou « u » est la densité totale d'énergie, « S » le vecteur de Poynting, « J » la densité de courant et « E » le champ électrique.

Plusieurs méthodes de mesure ont été mises au point par plusieurs pays, principalement en France, en Allemagne, en Italie, aux Eta-Unis et au Japon. Conduites entre autres par l'industrie automobile, la mise au point de ces méthodes de mesures fut un début de réponse aux problèmes d'influences électromagnétiques que connaissait cette industrie, et qui s'amplifiaient avec l'augmentation du nombre de circuits embarqués sur les automobiles.

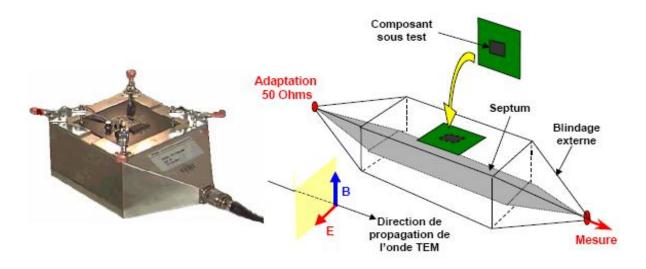

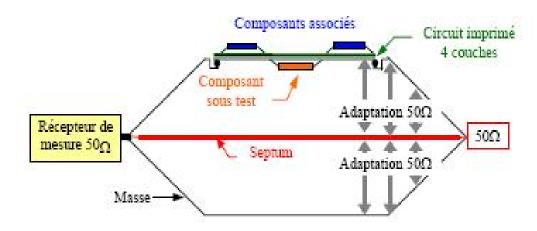

La SAE (Society of Automotive Engineers) a proposé une méthode utilisant une cellule TEM (figure II-1 [6]) pour la mesure des émissions rayonnées entre 150 kHz et 1 GHz. La cellule TEM, permet de réaliser les mesures d'émission propre d'un composant, en incluant la totalité de ses émissions, sans nécessiter l'utilisation d'une chambre anéchoïde ni d'antennes conventionnelles avec les limitations fréquentielles, les non-linéarités de phase, la directivité ou la polarisation qui leur sont propres. La cellule TEM (Transverse Electromagnetic Mode) est une ligne de transmission, adaptée  $50\Omega$  et élargie, qui propage l'onde TEM d'une source externe ou interne. Cette onde est caractérisée par des champs électriques (E) et magnétiques (H) orthogonaux entre eux et perpendiculaires à la direction de propagation le long de l'axe longitudinal de la cellule. [6]

Figure II-1: la cellule TEM

L'originalité de la méthode est que la carte carrée où est placé le circuit à tester ne sera pas mise à l'intérieur de la cellule, comme dans de nombreux tests de CEM, mais fera partie intégrante du blindage externe de masse de la cellule en le prolongeant. Seul le circuit intégré se trouve ainsi à l'intérieur de la cellule, les composants associés étant placés à l'extérieur (Figure II-2 [6]). Le septum, qui est la plaque métallique figurant l'âme de la ligne de transmission et assurant par sa géométrie l'adaptation  $50\Omega$  sur toute la longueur de la cellule, reçoit l'onde émise par le circuit et la propage vers le récepteur de mesure. [6]

Figure : Vue en coupe de la mesure en cellule TEM.

Analogue à la cellule TEM la GTEM permet d'augmenter cette gamme jusqu'à 24 GHz selon les modèles et le volume utile interne. La (figure II-3 [1]) illustre une cellule GTEM.

D'autres méthodes existent, nous pouvons ainsi citer celle basée sur le WBFC (Workbench Faraday Cage –voir figure II-4 [19]) qui a été proposée par un groupe néerlandais et qui reprend le principe de la cage de Faraday pour la mesure des émissions conduites entre 150 kHz et 1 GHz.

Figure II-4: Photo du Workbench Faraday Cage.

En octobre 1997, le sous-comité 47A de l'IEC a décidé de créer un groupe de travail (Working Group WG9) pour analyser les méthodes de mesure suggérées pour les circuits intégrés. Après une discussion approfondie, il a été décidé de créer une « boîte à outils » (tool box) de cinq méthodes pour évaluer la CEM des circuits intégrés : La mesure par une cellule TEM, la technique de scan surfacique, la méthode  $1\Omega/150\Omega$ , la technique de mesure utilisant la WBFC (Workbench Fraday Cage) et la méthode utilisant une sonde magnétique. [1]

#### II) Estimation des éléments RLC

La résistance, la capacité et l'inductance parasite des différents conducteurs peuvent être estimées à l'aide des équations suivantes :

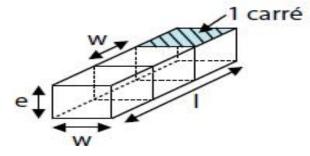

#### a) La résistance

L'évaluation des paramètres résistifs peut être obtenue en appliquant les formules considérant la résistance par carré (figure II-5 [4]). La résistance par carré,  $R_{\square}$ , correspond à une portion de conducteur dont la longueur est égale à la largeur, vu de haut. La résistance par carré est d'autant plus grande que la section du conducteur est faible.

$$R_{\square} = \rho \cdot \frac{1}{S} = \rho \cdot \frac{W}{W \cdot e} = \frac{\rho}{e}$$

Équation II-2 [4]

Avec:

e : épaisseur du métal (μm)

w: longueur d'un carré élémentaire (µm)

1: longueur totale du conducteur (μm)

S: section du conducteur ( $\mu m^2$ )

$\rho$  : résistivité du métal ( $\Omega.\mu m)$

Figure II-5 : principe de la résistance par carré

$\rho$ Al = 0,0277 Ω.μm résistivité de l'aluminium

$\rho$ Cu = 0,0172 Ω.μm résistivité du cuivre

$\rho$ Au = 0,022 Ω.μm résistivité de l'or

Quelque soit le type de boîtier considéré, la valeur de la résistance est généralement comprise entre  $50 \text{ m}\Omega$  et  $500 \text{ m}\Omega$ . A cause de l'effet de peau, la résistance tend à augmenter avec la fréquence. [4] [6]

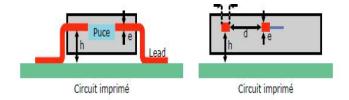

### b) La capacité

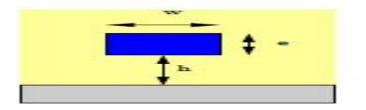

En considérant la figure II-6 [4] :

W: largeur du métal (µm)

e : épaisseur du métal (μm)

h: hauteur par rapport au substrat (μm)

d : distance séparant deux broches (μm)

Figure II-6 : capacité entre un conducteur (lead) et le substrat

Afin d'estimer la capacité d'un conducteur, un (lead) par exemple, il est possible d'utiliser la formule suivante :

Avec:

$\varepsilon_{\mathbb{Z}}$  et  $\varepsilon_{\mathbb{Z}}$  sont respectivement la permittivité du vide ( $\varepsilon_{\mathbb{Z}} = 8,85$  .10-12 F/m) et la permittivité relative de l'isolant (pour SiO2  $\varepsilon_{\mathbb{Z}} = 3,9$ ). De plus, ces formulations analytiques sont valables pour des rapports w/h et e/h supérieurs à 0,02 et inférieurs à 5,12. [4] [6]

### c) Løinductance

De même que la capacité et la résistance une formule nous permet de rendre compte de l'inductance d'un conducteur (bonding) en considérant le substrat relier au plant de masse on a alors :

d: diamètre du fil (m)

h: hauteur par rapport au plan de masse (m)

Figure II-7: Calcul de l'inductance d'un bonding. [4]

L 2

$$\mu_{\mathbb{Z}}\mu_{\mathbb{Z}}\frac{\mathbb{Z}}{\mathbb{Z}\pi}\ln\mathbb{Z}^{\mathbb{Z}}$$

Equation II-4 [4]

Où  $\mu_{\mathbb{Z}}$  et  $\mu_{\mathbb{Z}}$ sont respectivement la perméabilité du vide ( $\mu 0 = 1,257$  .10-6 H/m) et la perméabilité relative de l'air ( $\mu r = 1$ ). [4]

Il est aussi possible de calculer les paramètres inductifs des conducteurs de type interconnexion sur silicium en considérant l'équation II-5, illustrée par la figure II-8. [6]

$$L_{22} \ 2 \ \mu_{2}\mu_{2} \frac{2}{20} \ln 2 \frac{2}{2} \ 2 \frac{2}{20} \ 2 \ \text{Équation II-5 [6]}$$

W = largeur du métal (m)

h = hauteur par rapport au substrat (m)

Figure II-8 : Calcul de l'inductance d'un conducteur de type interconnexion au dessus d'un plan de masse.

Les valeurs typiques de l'inductance et de la capacité des boitiers les plus utilisés sont présentés dans le tableau II-1. [4]

| Boîtier              | Description                          | Capacité<br>d'un <i>lead</i> | Inductance<br>d'un <i>lead</i> |

|----------------------|--------------------------------------|------------------------------|--------------------------------|

| in minimi            | Dual in line<br>(DIL)                | 1 – 10 pF                    | 2 – 15 nH                      |

| Same memoral control | Shrink dual in line<br>(SDIL)        | 1 – 10 pF                    | 1 – 10 nH                      |

| ALCOHOL:             | Small outline package<br>(SOP)       | 1 – 7 pF                     | 1 – 7 nH                       |

|                      | Quad flat package<br>(QFP)           | 2 – 5 pF                     | 3 – 7 nH                       |

|                      | Bold gate array<br>(BGA)             | 1 – 10 pF                    | 0.5 – 10 nH                    |

|                      | Fine pitch ball gate array<br>(FBGA) | 1 – 20 pF                    | 0.5 – 10 nH                    |

|                      | Mold chip scale package<br>(MCSP)    | 1 – 15 pF                    | 0.5 – 5 nH                     |

Tableau II-1 : Capacité et inductance de boîtiers usuels.

# III) Standard IBIS et son utilisation en CEM des circuits intégrés

# a) Description

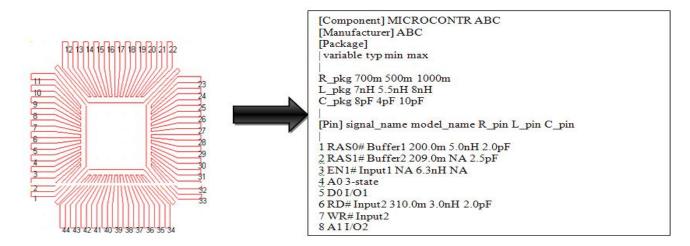

Le modèle IBIS (Input/Output Buffer Information Specification) a été créé par INTEL pour son processeur 80386 afin de pouvoir fournir à ses clients les caractéristiques des circuits d'entrée/sortie, sans révéler d'information technologique. Ce type de modèle est publique depuis juin 93 (version 1.1), il est devenu un standard de l'Electronic Industry Association (EIA) en mars 95 et a subi des améliorations successives jusqu'à la 4ème version (juillet 2002).

Le modèle IBIS est un modèle comportemental qui caractérise uniquement les entrées/sorties des composants numériques. Il permet de décrire un étage d'entrée/sortie sans avoir son schéma électrique ce qui garantit au fondeur la confidentialité de la structure interne et des paramètres technologiques. Ce modèle est particulièrement destiné à la simulation de cartes ou de systèmes complets, notamment au niveau de l'intégrité de signal (synchronisation,

délais, diaphonie...). Le fichier IBIS contient ainsi, dans un format ASCII, toutes les informations sur chacun des composants de ces modèles :

- le boîtier : $R_{2/2}$  ,  $L_{2/2}$  et  $C_{2/2}$

- les entrées et sorties : C

- les tableaux I (V) pour les diodes de protection reliées à la masse et au VDD.

- les tableaux I (V) pour les transistors Pull-up et le Pull-down en sortie de l'inverseur.

- les tableaux des temps de montée (dV/dt r) et de descente (dV/dt f).

Pour la plupart de ces données, le modèle nécessite des valeurs typiques, minimum et maximum. [6] [18]

Un exemple de description IBIS (partie initiale) d'un composant est donné Figure II-9 [6]. Il s'agit d'un fichier texte décrivant les structures actives des paramètres parasites du boîtier.

Figure II-9 : Description du boîtier et de la puce par le modèle IBIS.

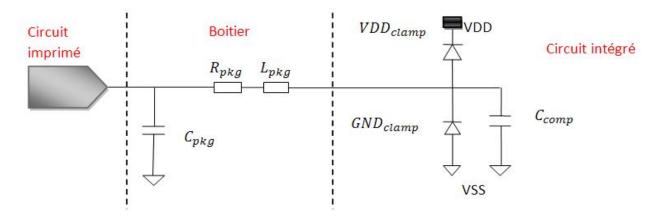

### b) Modèle IBIS døune entrée

Le modèle d'une entrée, (Figure II-10 [6]) est généralement constitué de :

- la liaison entre la puce et la broche externe (boîtier) : elle se caractérise par une capacité de boîtier  $C_{\text{DD}}$ , une résistance  $R_{\text{DD}}$  et d'une inductance  $L_{\text{DD}}$  incluant la piste du boîtier en fil d'or de liaison puce/boîtier (bonding).

Figure II- 10 : Modèle IBIS d'une entrée.

# c) Modèle IBIS døune sortie

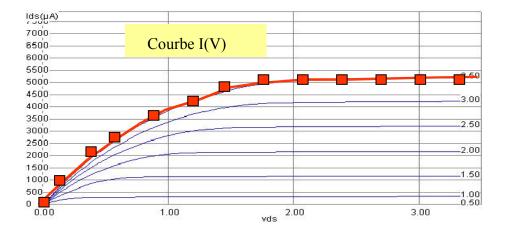

Plutôt que de fournir les paramètres SPICE pour différents modèles standards de dispositifs, le modèle IBIS donne la courbe de réponse I(V) de la sortie correspondant pour les buffers à VG = VDD (Figure II-11 [6]). Ceci permet une simulation assez précise tout en préservant le caractère confidentiel des paramètres technologiques et en étant indépendant du modèle et de son implémentation logicielle.

Figure II-11 : Caractéristique I(V) permettant de simuler la réponse d'une sortie tout en préservant la confidentialité des paramètres technologiques.

Ces données peuvent être déterminées soit par simulation réalisées par le fondeur pour VG = VDD, soit par mesure, en injectant une tension a la sortie et en mesurant le courant.

Le modèle d'une sortie est alors généralement constitué de (Figure II-12 [6]) : -La liaison entre la puce et la broche externe (boîtier)

-L'étage de sortie de la puce : il est modélisé par la capacité de sortie  $C_{\square\square\square}$  du composant, les diodes de protection l'un reliée à la masse et l'autre à l'alimentation VDD, et par les caractéristiques I(V) de pull-up et de pull-down de l'inverseur de sortie.

Figure II-12: modèle IBIS d'une sortie.

Il est à noter que le modèle IBIS renseigne également sur les caractéristiques dynamiques du composant, temps de monté, temps de descente des signaux, retards etc. On calcule par exemple les pentes de ces signaux temporels pour la transition de 20% à 80% (ou inversement) de la tension finale.

# d) Limites du modèle IBIS

Le modèle IBIS permet de simuler correctement les phénomènes d'intégrité des signaux malgré une représentativité limitée dans le domaine fréquentiel. Dans le cadre de composants simples, les résultats obtenus par la simulation sont en général relativement proches de ceux mesurés. Pour les simulations CEM le modèle IBIS est insuffisant. IBIS ne prend en effet pas en compte :

1. les sources de perturbations sur les entrées/sorties liées à l'activité interne du composant. Pour les composants à forte intégration cette activité est souvent à des fréquences beaucoup plus élevées que celles des signaux E/S. La Figure II-13 [6] illustre le fait que le spectre simulé est plus pauvre que le spectre mesuré.

Figure II-13 : spectre mesuré et simulé pour des composants complexes.

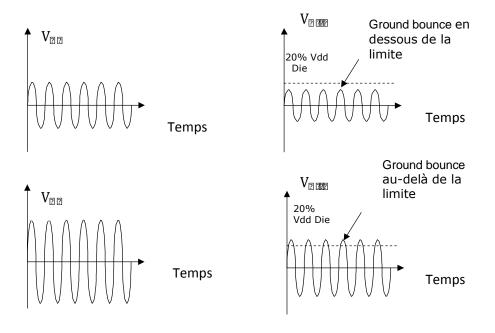

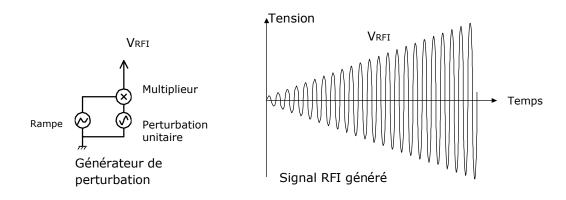

2. les variations du courant d'alimentation dues à la commutation simultanée des buffers et à l'activité interne du composant ne sont pas modélisées. Ces perturbations véhiculées par les alimentations (« Ground bounce » Figure II-14 [6]) ont un rôle prépondérant sur le comportement en rayonnement des circuits imprimés.

Figure II-14 : différence entre la forme d'onde simulée et celle mesurée.

3. le champ électromagnétique émis directement par le composant n'est pas traité. Les effets d'antenne des éléments boîtier, l'effet d'antenne du substrat de la puce, ou encore les boucles de courant interne à la puce notamment dans les rails d'alimentation ne sont pas modélisés.

### e) Modèle IMIC

Le modèle IMIC (I/O Interface Model for Integrated Circuits) est proposé par l'Electronic Industries Association of Japan (EIAJ) comme une amélioration du modèle IBIS actuel. Le modèle IMIC inclut la description des interconnexions qui lient à l'intérieur du composant les étages de sortie. Cette description des interconnexions est donnée au format SPICE. Il offre aussi la possibilité d'ajouter des stimuli sur les étages internes. De plus, il propose de dissocier le modèle en trois entités : la puce, le boîtier et le module (Figure II-15 [6]). Par ailleurs, il permet d'ajouter des informations de mutuelle inductance et mutuelle capacité entre les broches du boîtier. En outre, il est capable de générer un format IBIS. [18]

Le modèle IMIC propos

Figure II-15: modèle IMIC

-Le niveau de base considère l'intégrité du signal, et permet donc d'évaluer le bruit des signaux en partant des hypothèses suivantes : les circuits de masse et d'alimentation sont parfaits, et les structures de boîtiers sont simples. En conséquence, ce niveau est équivalent au modèle IBIS.

-Le niveau intermédiaire est basé sur l'intégrité de l'alimentation. Ici, il est possible de simuler les phénomènes de ground bounce et VDD bounce. Ces simulations sont menées en considérant des masses non idéales ainsi qu'une structure de boîtier plus complexe.

-Le dernier niveau prend en compte les aspects CEM, ce qui en fait le niveau le plus précis. En effet, il ne se contente pas de couvrir uniquement les deux précédents niveaux, mais prend en compte les aspects tridimensionnels de la structure du boîtier, ainsi que l'ensemble des courants qui s'écoulent à travers le composant.

Étant plus proche de l'implémentation physique du composant, le modèle IMIC présente l'avantage d'offrir des simulations plus précises que le modèle IBIS. De plus, il est possible de rajouter des générateurs internes. Cependant, ce modèle ne propose aucun moyen d'identifier et de quantifier ces sources internes. Enfin, certaines données prises en compte dans le modèle peuvent être considérées par le fondeur comme confidentielles : c'est le cas pour les résistances d'accès entre le plot et le buffer.

# IV) Modèle ICEM

- a) Besoins doun modèle de compatibilité électromagnétique

- 1) Format døchange fabricant utilisateur

Être capable de fournir un modèle CEM d'émission d'un composant est aujourd'hui un argument commercial pour le fondeur car il permet à l'équipementier de simuler son système électronique complet avant même qu'il ne soit fabriqué. L'équipementier peut ainsi s'assurer, sans campagnes de mesures coûteuses, de la conformité de son système en cas d'évolution technologique, et peut aussi prendre les dispositions nécessaires (circuits imprimés, composants de découplage, filtres), pour satisfaire aux normes de son équipement.

Le modèle doit donc tenir compte des contraintes de cet échange. Il doit être :

- -Non confidentiel

- -Rapide à simuler

- -Facile à mettre en œuvre

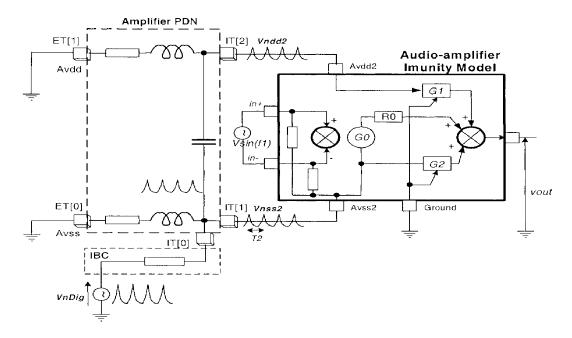

Les méthodes d'obtention des paramètres du modèle devront aussi être variées pour couvrir les situations diverses que sont le cas du fondeur, qui peut recourir à ses librairies technologiques et utiliser le modèle pour des simulations prédictives d'émission du composant, et le cas de l'utilisateur disposant de peu d'information sur son composant et souhaitant obtenir par la mesure les paramètres de ce modèle.