### République Algérienne Démocratique et Populaire Ministère de L'Enseignement Supérieur et de la Recherche Scientifique

Université Mouloud Mammeri De Tizi-Ouzou

## Mémoire de Fin d'Etude De MASTER ACADEMIQUE

Spécialité : Génie Microélectronique

Présenté par : HIKEM NOURA

### **Thème**

# Conception D'un transistor MOS SOI.

## Devant le jury :

| Mr. | K.HAMOUCHE | Professeur       | Président   | UMMTO        |

|-----|------------|------------------|-------------|--------------|

| Mr. | A.BENFDILA | Professeur       | Promoteur   | <b>UMMTO</b> |

| Mr. | A.LAKHLEF  | Maître Assistant | Examinateur | UMMTO        |

| Mr. | M.GOUDJIL  | D.Chercheur      | Examinateur | CDTA         |

**Première Promotion 2014**

## REMERCIEMENT:

Je remercie vivement mon promoteur monsieur Arezki Benfdila. Je tiens à lui exprimer ma profonde reconnaissance pour son soutien et les conseils qu'il m'a accordé tout au long de ce mémoire.

Je remercie monsieur Achour Hakim, monsieur Lakhelf qui ont apporté de l'aide à ce travail

Je remercie les membres de jury qui m'ont fait l'honneur de bien vouloir examiner ce travail

Enfin, j'exprime ma profonde gratitude à mes parents; ma mère en particulier, pour leurs efforts et la grande confiance témoignée depuis le début de mes études, sans oublier de remercier mes sœurs et frères

## Je dédie ce modeste travail

\*à ceux qui m'on donnée vie, mes chère parents

« maman »,

« papa » pour avoir tou jours été la pour moi, pour vous

bons conseils et soutien.

\*à mes frères adores « walid, hassain »,

\*a mes sœurs chéries « Amel, Katia »,

\*a ma grand mère que dieu vous protége,

\*à mon cher fiance « Ali »,

\*a mes copines « kahina,sabrina,amel,faiza,taous»,

Noura

## Introduction générale

## CHAPITRE I : LE TRANSISTOR MOSFET BULK ET SON EVOLUTION

| I.1: Introduction                                                     |

|-----------------------------------------------------------------------|

| I.2 : La Structure de la capacité MOS                                 |

| I.3 : Le transistor MOS : architecture et principes de Fonctionnement |

| I.3.1 : Présentation de l'architecture du transistor MOS              |

| I.3.2 : Les régimes de fonctionnement du transistor MOS bulk5         |

| I.4 : Les paramètres électriques du Transistor MOS                    |

| I.5 : MOSFET submicronique et les effets des canaux cours             |

| I.5.1 : Effets indésirables dans le transistor MOSFET à canal court9. |

| I.5.2 : SCE : effet de canal court (short channel effect)             |

| I.5.3 : Effet de DIBL (drain inducedbarrier lowering)                 |

| I.5.4 : Effet de Canal Court Inverse                                  |

| I.5.5 : Effets de porteurs chauds                                     |

| I.6: MOSFET Nanométrique                                              |

| I.7 : Limitations liées à la miniaturisation des dispositifs          |

| CHAPITRE II : PRESENTATION DE LA TECHNOLOGIE SOI                      |

| II. Introduction                                                      |

| II.1 : principe de fonctionnement du transistor à effet de champ      |

| II.2 : la technologie MOS SOI                                         |

| II.3 : Qu'est-ce que le SOI                                           |

| II.4 : Transistor Mos SOI partiellement et entièrement déserté        |

| II.5 : Les avantages de transistor MOS SOI vs BULK MOSFET             |

| II.6 : Les inconvénients de transistor MOS SOI24                      |

### Table des matières

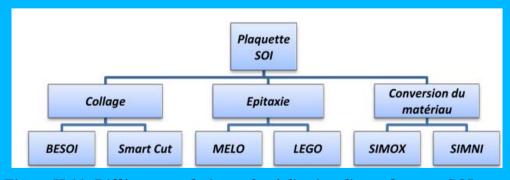

| II.7. Fabrication d'une plaquette SOI                                                  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|--|--|--|--|--|

| II.7.1. Technique de collage                                                           |  |  |  |  |  |

| II.7.2. Technique d'Epitaxie                                                           |  |  |  |  |  |

| II.7.3. Technique de conversion du matériau                                            |  |  |  |  |  |

| II.8 conclusion                                                                        |  |  |  |  |  |

| CHAPITRE III: LES STRUCTURES AVANCEES MULTI-GRILLE SOI                                 |  |  |  |  |  |

| III. Les transistors à grilles multiples                                               |  |  |  |  |  |

| III.I Avantages des transistors à grilles multiples                                    |  |  |  |  |  |

| III.2 La technologie SOI MOSET double-grille                                           |  |  |  |  |  |

| III.2.1 Introduction au transistor mos soi double grille                               |  |  |  |  |  |

| III.2.2 Le transistor double grilles planaire (linaire)                                |  |  |  |  |  |

| III.2.3 Transistor Gate All Around (GAA)                                               |  |  |  |  |  |

| II.2.4 Transistor double grille a conduction vertical                                  |  |  |  |  |  |

| II.2.6 Transistor DELTA-FET                                                            |  |  |  |  |  |

| II.2.7 transistor FinFET                                                               |  |  |  |  |  |

| CHAPITRE IV: ETUDE COMPARATIVE DE TRANSISTOR FD SOI ET PD                              |  |  |  |  |  |

| IV. Introduction                                                                       |  |  |  |  |  |

| IV.1. L'outil de simulation SILVACO                                                    |  |  |  |  |  |

| IV.2. Présentation du paquet des programmes SILVACO                                    |  |  |  |  |  |

| IV.2.1. Les outils de simulation ATLAS (de la société SILVACO)42                       |  |  |  |  |  |

| IV.2.2. Présentation d'Atlas                                                           |  |  |  |  |  |

| IV. 2.3. Logique de programmation                                                      |  |  |  |  |  |

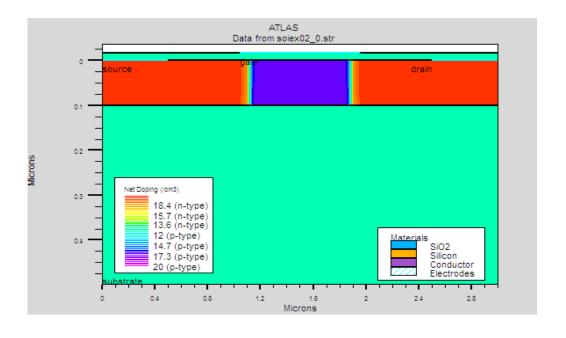

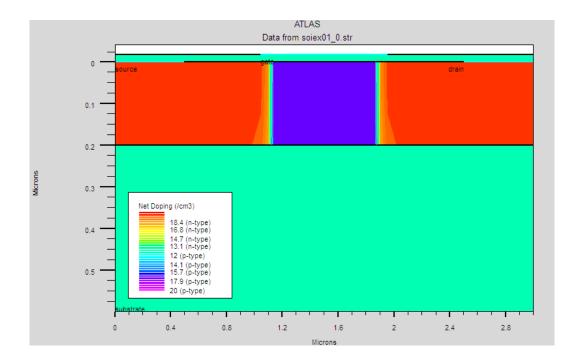

| IV.2.4. La simulation numérique d'une structure SOI MOSFET complètement déserté et SOI |  |  |  |  |  |

| MOSFET partiellement déserté 46                                                        |  |  |  |  |  |

### Table des matières

| Conclusion générale                                                            | 53  |

|--------------------------------------------------------------------------------|-----|

| Conclusion.                                                                    | 52  |

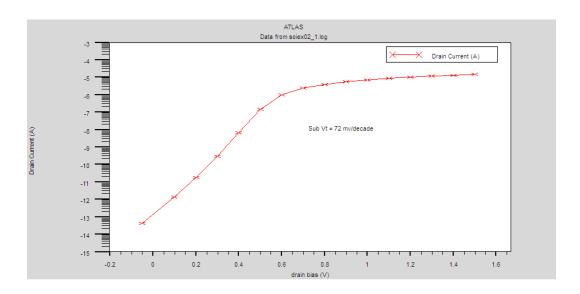

| IV.4 Résultats de simulation et interprétation                                 | 50  |

| IV.3. Choix des paramètres technologiques pour les structures FD SOI et PD SOI | .47 |

Depuis l'invention du transistor, un grand nombre de composants microélectroniques a été développé dans des laboratoires universitaires ou dans des sociétés de semi-conducteurs. Le composant de base qui est actuellement utilisé pour l'intégration à très grande échelle des circuits VLSI (Very Large Scale Integration), tels que les microprocesseurs et les mémoires, transistor MOS (Metal-Oxyde-Semiconductor). La technologie **CMOS** est (Complementary-Metal-Oxyde-Semiconductor) est devenue dominante et a été choisie historiquement en raison de sa propriété de faible consommation de puissance comparée aux autres technologies. Plus de 80% des circuits VLSI récents sont fabriqués avec la technologie CMOS. Les tendances générales en microélectronique sont à la réduction de la géométrie des transistors qui permet d'obtenir une augmentation des performances et de la densité d'intégration des dispositifs. En effet avec la miniaturisation, nous assistons à l'apparition de phénomènes d'ordre théorique remettant en cause les avantages qu'offrait la technologie CMOS[I.]. Parmi ces phénomènes, nous avons notamment l'abaissement de la barrière de potentiel au niveau du drain donnant naissance au phénomène dit DIBL (drain induced barrier leackage), les effets canaux courts dits SCE (short chanel affect), les phénomènes de nature quantique, le courant tunnel de grille, la fluctuation aléatoire des dopants[I.8]

De ce fait, de nouvelles approches sont nécessaires afin de continuer la réduction de la longueur de canal. Les structures et technologies silicium sur isolant (SOI) qui sont mise en en évidence dans les années 1960-1970 pour satisfaire la demande de circuits intégrés immunisés aux irradiations ionisantes.et multi-grilles (MUG-FET) apparaissent aujourd'hui comme les approches les plus prometteuses pour la fabrication de circuits intégrés à basse consommation, haute fréquence à des hautes ou basses températures.

Les technologies SOI sont aujourd'hui largement utilisées pour la réalisation de microprocesseur (IBM, AMD) ou pour la conception de circuit ASIC haute performance...ext [I.2].

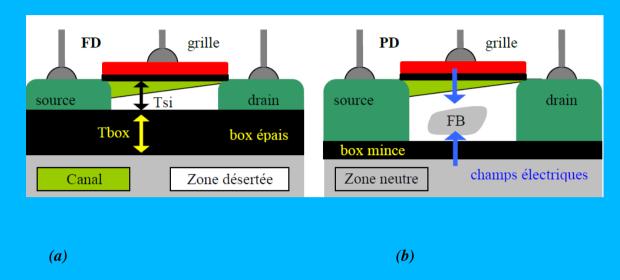

La première révolution dans l'architecture du transistor MOSFET est l'apparition des transistors sur film mince SOI. Ce type de transistor est caractérisé par deux paramètres supplémentaires par rapport aux transistors conventionnels : l'épaisseur du film Si (TSi) sur lequel est intégrée la région active du dispositif et l'épaisseur de la couche d'oxyde (TBOX) dit oxyde enterré. On distingue deux types de dispositif sur film mince. Lorsque l'épaisseur du film est suffisamment épaisse, une partie seulement du film est désertée. On parle alors du

#### Introduction Générale

transistor silicium sur isolant partiellement deplete PD-SO («Partialy Depleted Silicon On Insulator »), son fonctionnement et ses caractéristiques sont proches de ceux du transistor sur silicium massif.

Lorsque l'épaisseur TSi est plus fine, l'ensemble du substrat est déserté et on parle cette fois d'un transistor MOS SOI totalement déserté, FD-SOI (« Fully Depleted Silicon On Insulator»). ce dernier présente de nombreux avantages tels que l'obtention des jonctions ultraminces permettant un bon contrôle des effets de canaux courts.

Dans le premier chapitre nous présenterons brièvement le transistor à effet de champs(MOSFET) sur substrat silicium massif.et son principe de fonctionnement, et son évolution, ainsi que les problèmes engendrés par sa miniaturisation (les effets de la miniaturisation.

Puis dans le second chapitre, Nous évoquerons ensuite les solutions technologiques possibles pour répondre à ces problèmes. c'est la technologie MOS SOI (Silicon OnInsulator ). Nous y présentons ses avantages par rapport aux technologies CMOS sur substrat massif, puis les principales techniques de réalisation des substrats SOI.

Ensuite dans le quatrième chapitre nous présenterons un aperçu des différentes architectures multi-grille alternatives: les structures planaires, les architectures double-grille à conduction verticale et les transistors à conduction latérale de type FinFET.

Enfin le dernier chapitre est consacré la comparaison des caractéristiques électriques de deux structures FD SOI et PD SOI, et l'interprétation des résultats de simulation que nous avons obtenus après avoir présenté le simulateur de dispositif que nous avons utilisé ATLAS SILVACO.

#### I.1. Introduction

Les notions du transistor MOS (Metal Oxide Semiconductor) ont été brevetés par Lilienfield et Heil en 1930. Cependant des difficultés technologiques ont retardé sa réalisation pratique dûs principalement aux problèmes d'interfaces Si/SiO2. Par conséquent, il n'apparaîtra sous sa forme actuelle qu'en 1955 grâce à Ross. Cela bien après la réalisation par Shockley en 1947 du premier transistor de type bipolaire, pourtant théoriquement bien plus compliqué. C'est en 1960 que Kahng et Attala ont exhibé le premier transistor MOS sur Silicium en utilisant une grille isolée dont le diélectrique de grille était en oxyde de silicium SiO2. Le silicium fut un choix très avisé car c'est l'élément le plus abondant de la croûte terrestre, après l'oxygène. Dans ce premier chapitre nous présentons la structure MOSFET bulk et ses différents régimes de fonctionnement et les effets indésirables lies a sa miniaturisation.

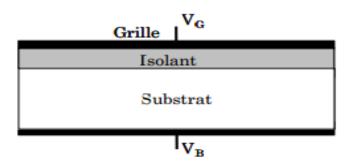

#### I.2. La structure de la capacité MOS

Par définition un condensateur est constitué de deux électrodes conductrices séparées par un matériau isolant. Ainsi, on appelle « capacité MIS » la superposition de trois couches de matériaux : le métal ou poly-silicium dégénéré (appelé grille), l'isolant (SiO2, HfO2, Ta2O5, Si3N4...), et le semiconducteur (Si, Ge...) de type N ou de type P (appelé bulk ou substrat) Figure I.1.

Figure I.1 Schéma en coupe d'une structure MIS

La dénomination capacité MOS (Metal-Oxide-Semiconducteur) résulte de la nature l'isolant qui est alors un oxyde.[1]

#### I.3 Le transistor MOS: architecture et principes de Fonctionnement

L'étude détaillée du MOSFET canal long est un préalable à la compréhension de tous les progrès réalisés à nos jours dans la miniaturisation du MOSFET. L'approche Top Down utilisée consistant en la réduction de sa géométrie en essayant de garder son comportement de MOSFET canal long (En minimisant notamment les Effets de canal Court indésirable qui apparaissent au fur et à mesure que l'on réduit les dimensions du MOSFET).

Cette étude commence tout d'abords par l'analyse du transistor MOSFET en général, notamment sa structure et son principe de fonctionnement. Nous nous intéresserons à ses courbes caractéristiques, ses paramètres physiques et électriques dans le cas du transistor à canal long ( $L > 100 \, \mu m$ )

#### I.3.1. Présentation de l'architecture du transistor MOS

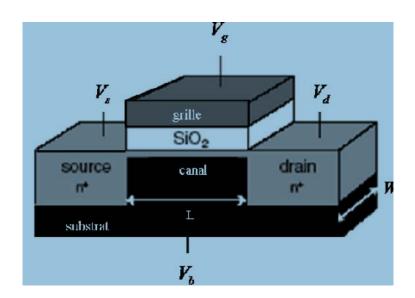

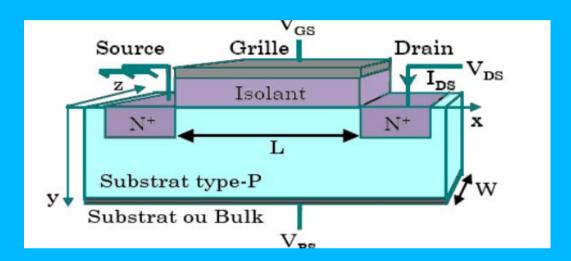

La structure de base du transistor Métal Oxyde Semi-conducteur à effet de champ (MOSFET) est représentée par la Figure I-2.

Figure I.2 Schéma d'un MOSFET de type N.

Nous présentons dans ce qui suit un transistor MOSFET à canal de type n .Ce transistor est réalisée à partir d'un substrat semi-conducteur, généralement de type P, dans lequel deux régions implantées N+ définissent la source et le drain. L'électrode de grille est obtenue à partir d'un oxyde (SiO2) recouvert par une couche de polysilicium fortement dopée. Les principaux paramètres géométriques du composant sont : L (longueur de grille, distance drain-

source), W (largeur transversale de la structure) et Tox (épaisseur d'oxyde). Dans les circuits intégrés, le transistor MOS est généralement isolé des composants voisins par des tranchées d'isolation. La zone active du transistor MOS est la région semiconductrice (substrat) située entre la source et le drain près de l'interface oxyde-semiconducteur [I.1]. La tension appliquée entre la grille et le substrat génère Vgb un champ électrique dans le substrat, et pour une tension Vgb suffisante, un canal de conduction est créé à l'interface oxyde-semiconducteur. Lorsque nous polarisons le transistor par une tension VDS, un courant de porteurs minoritaires circule dans le canal entre la source et le drain. Nous parlons de transistor NMOS lorsque le substrat est dopé avec des atomes accepteurs et que les porteurs minoritaires sont les électrons. Dans ce cas, les régions de source et de drain sont fortement dopées avec des atomes donneurs (i.e. une conduction assurée par des électrons). Le transistor pMOS possède un substrat dopé avec des atomes de type donneur et les porteurs minoritaires sont les trous.

#### I.3.2. Les régimes de fonctionnement du transistor MOS bulk

Les différents régimes de fonctionnement sont définis suivant les valeurs du potentiel de surface et selon la polarisation de la grille . Ici ces régimes sont définis dans le cas du transistor NMOS [I.4] , il existe quatre régimes de fonctionnement du transistor MOSFET .

La charge dans le semi-conducteur est dominée par les porteurs majoritaires du substrat (les trous) près de la surface. Les porteurs sont attirés très près de l'interface diélectrique/semiconducteur. La charge à la surface du semiconducteur est du même type que le volume du semiconducteur avec une densité de trous à la surface grande devant la densité de trous dans le volume.

#### $\triangleright$ Régime de bandes plates: Ψs = 0

Ce régime est le seul cas dans lequel le semi-conducteur conserve jusqu'à la surface ses propriétés de volume.

#### **Régime de désertion:** $0 < \psi s < \Phi fb$ Soit VG > VFB

Les porteurs majoritaires sont repoussés de l'interface. Il se crée alors près de la surface une zone dépourvue de porteurs libres (électrons et trous), appelée zone de charge d'espace. Cette

zone est constituée uniquement d'impuretés ionisées (charges négatives).Durant ces deux régimes (accumulation et désertion), le transistor est bloqué.

#### $\triangleright$ Régime d'inversion faible: $\Phi f < \psi f < 2\phi f$ soit Vfb< Vg < Vt

Pour Ψs=Φf, les densités d'électrons et de trous sont égales en surface (près de l'interface oxyde/semi-conducteur) à la densité intrinsèque de porteurs du matériau considéré (ni).

A partir de  $\Psi$   $s>\Phi f$ , les porteurs présents en plus grande quantité à la surface sont des électrons. Durant le régime d'inversion faible, la densité de porteurs majoritaires à la surface (électrons) est toujours inférieure à la densité de porteurs majoritaires dans le volume (trous).

#### Remarque

La tension de seuil est la valeur de la tension de grille pour laquelle le transistor passe du régime d'inversion faible au régime d'inversion forte.

#### Régime d'inversion forte: $\psi f > 2\phi f$ soit Vfb $\langle Vgt \langle Vt \rangle$

Les électrons sont les porteurs présents en plus grand nombre à la surface et en densité supérieure à celle des trous dans le volume du semi-conducteur. Les porteurs libres sont présents en grand nombre dans le canal. Le transistor est passant.

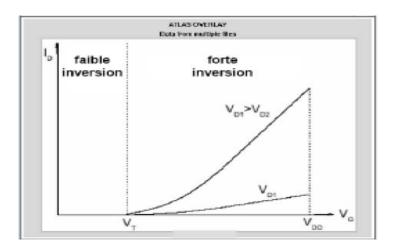

#### I.3.3 caractéristique Id-Vg

Sur la caractéristique Id-Vg (Figure I.3), nous distinguons deux niveaux d'inversion. La tension de seuil *Vth* que l'on détaillera dans ce qui suit représente la tension appliquée entre la grille et le substrat à partir de laquelle le transistor commence à conduire. Elle sépare la région de faible inversion (ou région sous le seuil) de la région de forte inversion (ou région au delà du seuil).

Figure I.3 : Caractéristique I d -V g du transistor NMOS avec les niveaux d'inversion.

Lorsqu'une différence de potentiel Vds est appliquée entre le drain et la source, un courant peut circuler dans le canal. La condition pour laquelle s'effectue l'inversion est ;

$$\Psi_S > \Phi f$$

-Ψs le potentiel de surface et  $\Phi F$  correspondant à l'écart entre le potentiel intrinsèque Ei/e et le potentiel de Fermi  $E_{fp}/e$  du semiconducteur dopé de type accepteur.

-  $\Phi F$  s'exprime comme

$$\Phi_{f} = \frac{K.T}{e} \cdot \ln \cdot \left( \frac{NA}{Ni} \right)$$

I.I

Où NA est la concentration des dopants du substrat et n i est la concentration intrinsèque du silicium. L'inversion forte à son tour apparaît lorsque :

$$\Psi_S > 2.\Phi_f$$

Dans ce cas, compte tenu que la couche conductrice d'inversion le volume du semiconducteur,  $\Psi S$  reste équivalent à  $2.\Phi F$ , en première approximation. La distinction entre ces deux régions de fonctionnement, la faible inversion et la forte inversion, nous amène à définir un paramètre important qui est la tension de seuil.

#### b)La tension de seuil

La tension de seuil est l'un des paramètres essentiels de fonctionnement du transistor MOS. Elle est définie comme étant la tension à appliquer à la grille pour obtenir la forte inversion, c'est-à-dire :

$$\Psi_{\rm S} > 2.\Phi f$$

Sous cette condition, la tension de seuil s'exprime comme suit :

Vth=Vfb + 2.

$$\Phi$$

f +  $\frac{\sqrt{4.e.\Phi f.NA}}{cox}$ .

$$V_{FB} = \phi_{ms} - \frac{Q_{SS}}{C_{ox}}$$

Avec

$$Vfb = \Phi m - \Phi si$$

$\Phi m$ et  $\Phi m$  sont tels que e.  $\Phi m$  et e.  $\Phi si$  représentent respectivement les travaux de sortie de la grille et du silicium,  $\varepsilon Si$  est la constante diélectrique du silicium, et enfin  $Cox1 = \varepsilon ox/tox$  désigne la capacité de l'oxyde. Cette expression de V th (1.4) est valable pour le transistor MOS bulk à canal long.

#### I.4. Les paramètres électrique du Transistor MOS

On définit les paramètres électriques nécessaires permettant d'exprimer l'équation du courant IDS comme suite.

• La transconductance ou gain (gm) est définie par

$$gm = (\frac{dIDS}{dVGS})$$

Vds :consatante Equ 1.6

Elle doit être la plus élevée possible. La transconductance augmente très rapidement lorsque la longueur de canal devient inférieure à 100 nm [I.2].

• La conductance du canal (gDS) donnée par :

$$gDS = \left(\frac{dIDS}{dVDS}\right)$$

Vgs : constante Equ 1.7

• La pente sous le seuil : elle représente la tension de grille à appliquer (en régime sous le seuil) pour augmenter le courant de drain d'une décade :

$$S = \frac{dVG}{dlog \ Id}$$

I.8

#### • Notion de la mobilité

La mobilité traduit l'aptitude des porteurs à se déplacer sous l'effet d'un champ électrique. C'est un paramètre très important des transistors MOSFETs car elle gouverne la valeur du courant de drain à polarisation fixe. La mobilité dépend de nombreux paramètres : champs électriques (longitudinaux et transverses), orientation du cristal, dopage du substrat, température

#### • b) La tension de seuil

La tension de seuil est l'un des paramètres essentiels de fonctionnement du transistor MOS. Elle est définie comme étant la tension à appliquer à la grille pour obtenir la forte inversion, c'est-à-dire :

$$\Psi_{S} > 2.\Phi f$$

#### I.5. MOSFET submicronique et les effets des canaux cours

Pour améliorer les performances notamment en fréquence des MOSFETs et pouvoir réaliser des fonctions électroniques de plus en plus complexes par l'augmentation de la densité d'intégration, les dimensions des dispositifs sont de plus en plus réduites et ont conduit au développement de dispositifs fortement submicroniques. Cependant, cette réduction d'échelle est source d'effets indésirables propres aux dispositifs de petites tailles et affectant sévèrement les performances espérées.

La conception et l'élaboration de MOSFET submicroniques nécessitent des paramètres supplémentaires comparés à ceux requis pour le cas du MOSFET à canal long. Essentiellement, on distingue :les profils des dopages au niveau de la source et du drain,

- le profil du dopage du canal,

- la construction des contacts

- la géométrie à la périphérie de la grille,

- Ces paramètres secondaires deviennent importants dans la conception et les procédés de fabrication y'influent beaucoup. Les critères de base employés pour optimiser la miniaturisation sont :

- Non uniformité du dopage du substrat : plus important entre la source et le drain qu'en dessous. Dans l'expression de  $L_{min}$ , c'est le dopage entre la source et drain qui est pris en considération.

- -Une couche légèrement dopée P sous la source et le drain réduit les capacités jonctions substrat et augmente la vitesse de réponse.

- -La structure des contacts aide aussi à réduire les capacités (surface de contact réduite).

- -L'extension de la jonction réduit les capacités parasites de recouvrement entre la grille et les jonctions. C'est cette profondeur de jonction qui est utilisée dans l'expression de  $L_{\min}$ .

- -La réduction des résistances séries constitue l'un des points les plus importants pour le développement de transistors submicroniques. Pour éviter d'avoir des résistances séries de jonctions importantes, on peut agir sur plusieurs facteurs (dopage des jonctions, surélévation des zones de source et drain, ...).

- -Utilisation de matériaux à faible résistivité pour la réalisation des interconnexions, par exemple, l'utilisation du cuivre (résistivité = 200.cm) à la place de l'aluminium (résistivité = 3.cm) engendre plusieurs avantages, notamment la réduction du coût de fabrication, la réduction de la consommation en puissance et la réalisation de lignes métalliques plus fines.

- -Le dopage de substrat doit être régit par la relation  $N_{sub} >= N_{canal} / 10$

- -La grille doit avoir une faible résistance /carrée et l'oxyde de grille doit être très fin et à faible densité de défauts. Ceci pour réduire le courant tunnel et augmenter la fiabilité de l'oxyde.

#### I.5.1- Effets indésirables dans le transistor MOSFET à canal court

En plus des instabilités dues aux charges d'oxyde, états d'interface, rugosités de surface, pour ne citer que ces instabilités, la réduction de la géométrie du transistor MOSFET fait aussi apparaître des effets indésirables qui dégradent les performances des dispositifs à canal court.

Si les manifestations de ces effets sur le fonctionnement du transistor peuvent être considérées comme étant de second ordre lorsque les dimensions sont microniques, pour des transistors

fortement submicroniques (W ;  $L << 1~\mu m$ ), ces effets peuvent dominer complètement le fonctionnement du dispositif et le rendre peu utilisable. Ainsi parmi les principaux effets :

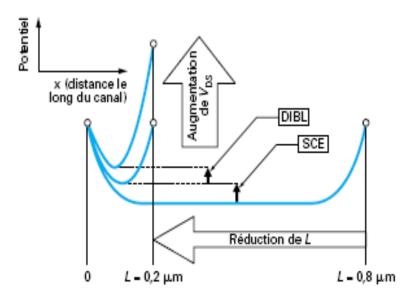

#### I.5.2 SCE: effet de canal court (short channel effect):

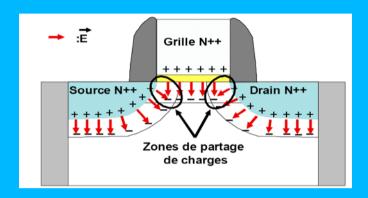

De manière générale, les effets canaux courts que nous noterons SCE (*Short Channel Effects*) constituent tous des effets parasites qui influent sur Vth .Deux effets parasites sont prédominants lorsque l'on atteint des dimensions très faibles : le partage de charge CS (Charge Sharing ou Roll-off) et le DIBL (Drain Induced Barrier Lowering).

Dans un transistor à canal court, comme les zones de charge d'espace S/D se rapprochent, on provoque une courbure et un abaissement du potentiel qui est plat sur presque toute la longueur du canal pour un MOSFET canal long, voir figure I.4 C'est l'effet de canal court

Figure I.4: Évolution du potentiel surfacique en fonction de la longueur du canal et du potentiel du drain

Cet abaissement de la barrière de potentiel entre de drain et la source augmente le courant et réduit la tension de seuil. Réduction donnée par la relation :

#### I.5.6 Effet de DIBL (drain induced barrier lowering)

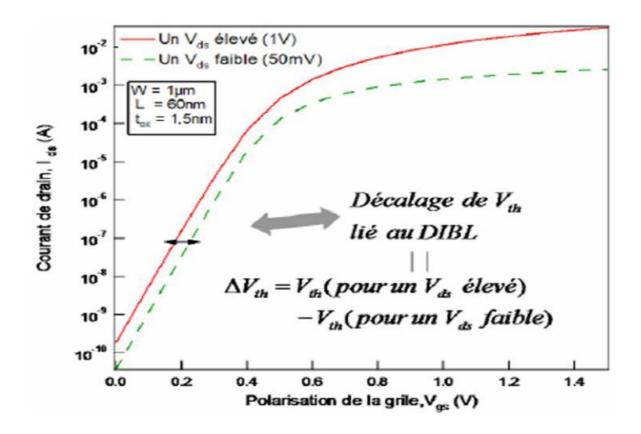

Pour expliquer l'effet du DIBL, nous devons considérer un dispositif à canal court. Lorsqu'aucune polarisation n'est appliquée, le profil de potentiel est le même que dans le cas du dispositif à canal long. Cependant, avec une tension de drain appliquée Figure II.5 suivante, le profil du potentiel de canal est affecté. La polarisation de drain change le profil sur toute la longueur du canal, abaissant la barrière à la jonction substrat-source. C'est effectivement un tel effet qui est référé comme étant l'abaissement de la barrière induite par le drain, ou le DIBL. Pour une tension de drain croissante, nous assistons à une traversée du canal par les porteurs à une valeur de polarisation de grille nettement inférieure à celle que l'on aurait eu en l'absence de cet effet dit DIBL. L'injection augmentée d'électrons par la source, par-dessus la barrière réduite, lorsque *Vds* augmente, entraine une croissance du courant de drain et donc une décroissance de Vth

Ce résultat s'observe bien sur la caractéristique Id –Vg en échelle logarithmique tracée à la Figure I.5.

Figure 1.5 Influence de l'effet du DIBL sur la caractéristique (Id -Vg) du transistor MOS

#### I.5.1.6 Effet de Canal Court Inverse

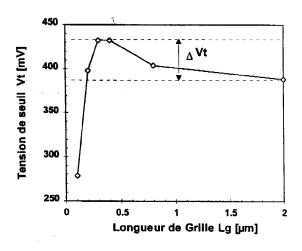

Il a été observé qu'une réduction de la longueur du canal pour augmenter la densité d'intégration entraînait une augmentation de la tension de seuil qui, à première vue, devait diminuer. Ainsi, cette observation a motivée l'étude du phénomène inverse de réduction de longueur du canal (RSCE : Reverse Short Channel Effect).

Ce phénomène est illustré par la figure I.6. On remarque qu'à certaines valeurs de la longueur de canal L la tension de seuil présente des valeurs maximales. Pour de très faibles valeurs de L (Deep Submicron MOSFETs) la tension de seuil augmente avec la longueur du canal L.

Figure I.6 : Variation de la tension de seuil avec la longueur de grille illustrant l'effet de canal court inverse

On définit la grandeur  $\Delta V_T$  comme étant la variation de la tension de seuil d'un transistor de longueur de canal L par rapport à un transistor de référence.

#### I.5.7. Effets de porteurs chauds

Quand on réduit la longueur du canal et que l'on augmente la tension de drain, le champ longitudinal prend des valeurs importantes et génère des porteurs dits chauds. Ces porteurs sont appelés ainsi car ils ont acquis une grande énergie qui ne peut être totalement dissipée à leurs arrivés à destination. Ils causent ainsi des dégradations au moment du transfert

de leur excès d'énergie au réseau du matériau constituant le MOSFET. Ces porteurs sont à l'origine de plusieurs effets néfastes pour le transistor.

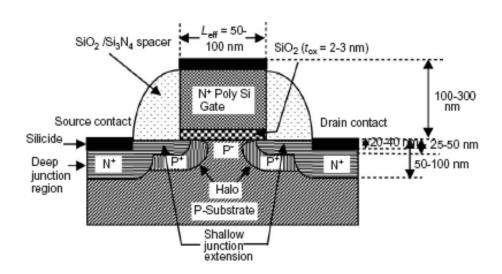

#### I.6. Le MOSFET nanométrique

Si de nos jours, l'industrie fabrique des transistors avec des longueurs de canal de 22nm, FinFET, L'ITRS (International Technology Roadmap for Semiconductors) prévoit des longueurs de grilles de 7nm en 2018. Pour ce faire, il existe plusieurs voies, notamment l'utilisation de nouvelles architectures qui devraient remplacer à plus au moins longue échéance le MOSFET conventionnel, et la réalisation de différent type de transistor selon l'application: hautes performances (HP) pour les microprocesseurs, basses consommations en fonctionnement (LOP) ou en état de veille (LTSP) pour les équipements portables.

Figure I.7: structure et dimensions typique du nanoMOSFET

La figure (I.7) illustre le nanoMOSFET typique fabriqué actuellement. Le dopage du canal est à profile rétrograde à fort dopage subsurfacique (5.10<sup>17</sup> à 3.10<sup>18</sup> cm<sup>-3</sup>) pour empêcher le champ électrique de drain d'arriver à la source (perçage volumique) et un faible dopage de surface (10<sup>17</sup> cm<sup>-3</sup>) pour maintenir une faible tension de seuil et améliorer la mobilité dans le canal en y réduisant les centres de collisions. Alors que des extensions de jonctions très minces sont utilisées pour le contact du canal avec le Drain et la source, des jonctions plus profondes sont utilisées pour établir la connexion avec les contacts métalliques drain source et ceci dans le but de réduire les résistances d'accès. Pour sa haute solubilité et son faible coefficient de diffusion, c'est l'arsenic qui est utilisé pour le dopage.

#### I.7. Limitations liées à la miniaturisation des dispositifs

Plusieurs raisons expliquent la volonté de diminuer les dimensions des transistors comme mentionné avant. La raison principale de la réduction des dimensions est l'intégration d'un plus grand nombre de dispositifs dans une même puce. Des dispositifs de dimensions réduites conduisent soit à une puce avec les mêmes fonctionnalités sur une surface plus petite, soit à des puces avec plus de fonctionnalités sur une même surface. Si on suppose que les coûts de fabrication d'une plaque microélectronique sont relativement fixes, le coût par circuit intégré est principalement lié au nombre de puces produites par plaque. Augmenter le nombre de puces par plaque permet donc de réduire le prix d'une puce. Ainsi, durant les trente dernières années, le nombre de transistors par puce a doublé tous les deux-trois ans à chaque introduction d'un nouveau nœud technologique. Cette tendance avait été anticipée par la loi de Moore basée sur un modèle économique et énoncée en 1965.

La diminution des grandeurs géométriques des transistors MOSFETs fût la première méthode utilisée pour améliorer la vitesse de commutation des transistors. Les MOSFETs de l'état de l'art sont maintenant fabriqués avec des longueurs de grille effective d'une dizaine de nanomètres seulement (environ 30nm en production), poussant les technologies conventionnelles à base de silicium dans le régime de la nanoélectronique.

Ceci a créé de nouveaux challenges pour modifier les autres dimensions des dispositifs, qui doivent être réduites en accord avec la longueur de grille. De nouveaux défis technologiques apparaissent avec la réduction des dimensions des dispositifs. Par exemple, l'épaisseur de l'oxyde de grille tox doit être réduite comme les autres dimensions du transistor, ce qui conduit notamment à des fuites de grille. Le dopage du substrat doit être augmenté, entraînant une augmentation des collisions entre les porteurs et donc une dégradation de la mobilité. Pour continuer à améliorer les performances des dispositifs, de nouvelles structures et des matériaux nouveaux ont été proposés. Ceci fait l'objet de la partie suivante.

#### II. Introduction

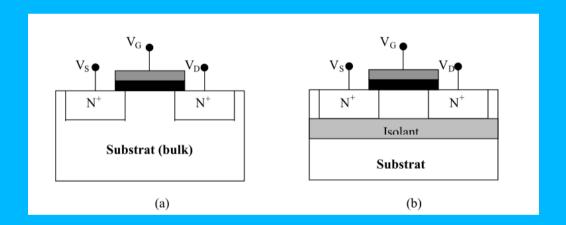

Afin de limiter les effets néfastes dus à la miniaturisation des transistors MOSFETs, des ajouts sont couramment utilisés dans les technologies les plus avancées pour améliorer les performances du transistor à savoir l'amélioration du contrôle électrostatique en créant de nouvelles architectures, la réduction des fuites de grille en utilisant de nouveaux matériaux et d'autres solutions technologiques pour l'amélioration des propriétés du transport des porteurs, La première révolution dans l'architecture du transistor MOSFET est l'apparition des transistors sur film mince SOI (« Silicon On Insultor ») .

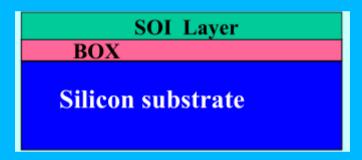

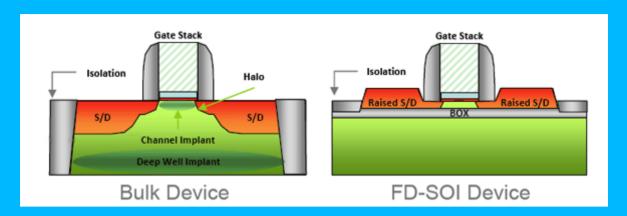

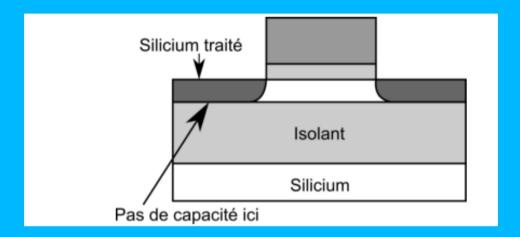

L'architecture des transistors MOS SOI (SOI MOSFET) est semblable à celle des transistors MOS sur Si massif (Si MOSFET) sauf que le substrat possède une couche d'oxyde enterré ("BOX" de l'anglais: Buried OXide) dans le silicium. On obtient ainsi un film de silicium confiné entre l'oxyde enterré et celui de la grille, ce qui a donnes de nombreux avantages pour ce dernier comme le montre la figure si dessous figure [I1] :

Figure II: vue en coupe de transistor SI-BULK(a) et MOS SOI (b)

#### II.1. Les transistors à effet de champ

Un transistor est avant tout un interrupteur commandé : un signal électrique (courant ou tension) de faible puissance, dit interrupteur de commande, doit contrôler un signal électrique de plus forte puissance.

Cela permet deux types de fonctionnement : soit en amplification pour les applications de type analogique, soit en tout ou rien pour les applications logiques ou

numérique. La structure Bulk-MOSFET est une structure qui nécessite plusieurs étapes pour la réalisé: tout d'abord on doit réaliser le type de substrat type-P ou type-N a savoir son fonctionnement, comme la montre la figure I.2 si dessous, on a choisis une substrat de type-P, à canal N, il possède 4 électrodes: la source et le drain qui sont les électrodes de puissance, la grille de longueur LG qui est l'électrode de commande, et le contact de substrat. L'isolant de grille en oxyde de silicium SiO2, La longueur du transistor notée L correspond à la longueur de sa grille et la largeur est notée W [1.7].

Figure II.2: vue schématique de transistor BULK MOSFET

#### II.2. la technologie mos soi

Afin de répondre aux besoins d'accroissement de la densité d'intégration et d'éliminer plusieurs problèmes liés au substrat massif dans les technologies nanométriques, la technologie silicium a évolué vers la technologie MOS SOI.

#### II.3. Qu'est-ce que le SOI:

Le matériau le plus utilisé actuellement dans la microélectronique pour la fabrication de circuits intègres est le silicium massif. Dans les transistors MOS réalisés sur SI massif, seule une région très fine (canal d'inversion). Près de l'interface, est utilisée pour la conduction électrique le reste de la plaquette n'étant pas utilisé, contrairement à la technologie SI massif, seule une région très fine(canal d'inversion), prés de l'interface, est utilisée pour la conduction électrique, le reste de la plaquette n'étant pas utilisé. Contrairement a la

technologie Si massif, le matériau SOI est constitué d'un empilement de trois couches comme le montre la figure au dessous :

a)SOI layer ou film de silicium monocristallin, sur lequel sont réalisés les circuits intégrés et qui est la seule couche active (qui participe effectivement au fonctionnement des dispositifs).

b) une couche isolante ou BOX (burierd oxyde) qui peut être ;soit un substrat épais complètement isolant, par exemple en saphire (AL2O3).

Soit une couche mince isolante (de 50nm a quelques Um), réalisée en oxyde de silicium (SiO2) et appelée oxyde enterré, qui sépare le film de silicium du substrat Sous-jacent

c) une couche épaisse de silicium, appelée substrat qui participes au fonctionnement des dispositifs et qui joue un rôle essentiellement mécanique [I.8]

Figure II.3 : Structure schématique des matériaux Silicium sur Isolant.

#### II.4: Transistor Mos SOI partiellement et entièrement déserté

Il existe plusieurs types de technologies SOI, On peut classer les transistors SOI en deux catégories suivant l'épaisseur de la zone désertée du film de silicium, soit PD partiellement dé OU FD complètement déserté suivant l'épaisseur de la zone désertée du film de silicium, donnée par la relation suivante

$$dmax = \sqrt{\frac{4.\Phi f.\varepsilon SI.}{qNa}}$$

où  $\Phi F$  est le potentiel de Fermi du silicium,  $\epsilon Si$  est la permittivité et Na est le dopage en ions accepteurs du film de silicium .Le transistor est qualifié de partiellement déserté (PD) si

l'épaisseur du film de silicium est plus importante que dmax (ce qui correspond au MOSFET sur substrat massif, et de totalement déserté (TD) dans le cas contraire. Les propriétés électriques sont différentes dans chacun des deux cas.

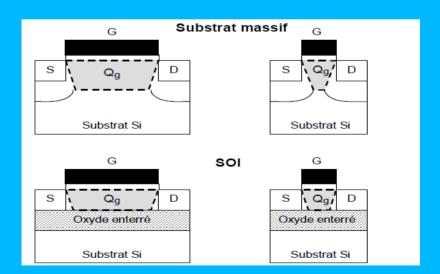

Figure II.4 : Représentation schématique d'un transistor MOS SOI : totalement désertés (a) Et partiellement désertés (b).

Pour les transistors SOI partiellement désertés, le film actif de silicium présente une zone interne neutre, située entre la zone de désertion et la couche d'oxyde enterré, qui empêche toute interaction entre les faces avant et arrière du transistor. Cependant, son potentiel est flottant puisqu'elle n'est reliée à aucun accès du transistor. Cela induit des phénomènes particuliers, tels que l'effet « kink » (II.4) et le transistor bipolaire parasite (II.4), qui sont fortement réduits dans le cas des transistors totalement désertés qui n'ont pas de zone interne flottante.

#### II.4.1. Les Transistors FDSOI

Les plaques de semi-conducteurs (wafers) SOI sont désormais considérées comme la technologie émergente de wafer la plus importante destinée à la production de circuits intégrés de pointe durant les 3 à 5 prochaines années . Les avantages de la technologie SOI proviennent de sa couche d'oxyde enterrée « BOX » (pour Buried OXyde) (Figure II. 6). Les transistors MOS fabriqués en technologie FD SOI reposent sur un film mince de silicium non dopé isolé du substrat par une couche d'oxyde de silicium.

Figure II.4.1 : Schéma illustrant l'architecture d'un transistor MOS sur substrat massif et sur SOI.

#### II.5. Les avantage de transistor MOS SOI vs BULK MOSFET.

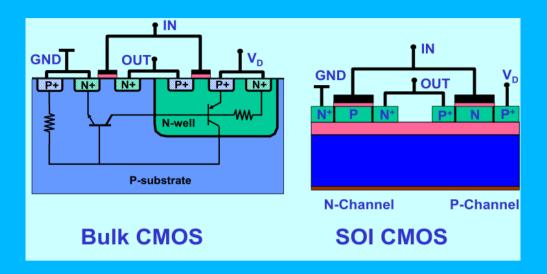

Les transistors MOS sur substrat massif (« bulk ») sont réalisés à la surface de la tranche de silicium, appelée couche active. L'épaisseur nécessaire pour réaliser le transport des électrons est très fine, de 0,1 µm à 0,2 µm , alors que les tranches de silicium ont une épaisseur de 800 µm. Le volume inactif du transistor, qui représente plus de 99,9 %, sert de support mécanique pour manipuler le transistors et les mettre en boîtier. Ce substrat inactif induit des phénomènes parasites, tels que des courants de fuite dans le substrat et des capacités de jonctions élevées comme mentionne dans le chapitre I. Les transistors MOS silicium sur isolant (SOI) reposent sur le principe de l'isolation diélectrique complète du composant, par un oxyde enterré sous sa zone active. L'isolation ainsi obtenue est largement supérieure à celle obtenue avec des techniques classiques sur substrat massif. Cette propriété confère au SOI de nombreux avantages en termes de performances : rapidité, faible consommation, immunité aux radiations Quelques-uns des avantages des transistors MOSFET sur SOI par rapport aux MOSFET sur substrat massif seront présentés dans les paragraphes suivants.

#### II.5.1. Haute fréquence

La fréquence de fonctionnement dans les circuits logiques dépend des temps de propagation ou des temps de commutation. Ces paramètres sont proportionnels à la capacité de sortie du transistor. Les capacités source/substrat (CJS) et drain / substrat (CJD) dans la technologie SOI sont 4 à 7 fois plus faibles que sur silicium massif (Figure 4). Tandis que sur silicium massif CJS (resp. CJD) équivaut à la capacité d'une jonction polarisée en inverse,

dans le SOI CJS (resp. CJD) est dominée par la capacité de l'oxyde enterré sous la source (resp. le drain), qui est beaucoup plus faible. La réduction des capacités parasites se répercute au niveau du circuit et améliore les performances en hautes fréquences des SOI MOSFET par rapport au silicium massif

Figure II.5 MOS a substrat SOI

Les propriétés électriques de cette structure, en particulier du transistor SOI entièrement déserté (fD SOI) , sont dans l'ensemble bien meilleures comparées au transistor BULK MOSFET, Il est d'ailleurs estimé que ce composant est un candidat susceptible de réussir l'intégration des dispositifs de dimensions longitudinales inférieures ou égales à 30nm

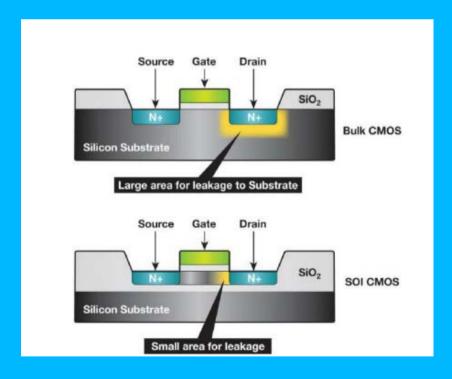

II.5.2. Réduire les effets des porteurs chauds. La technologie SOI permet la réduction des effets des porteurs chauds: dans les FD MOSFET, le champ électrique transversal est réduit vu que la zone de déplétion se limite à l'épaisseur du film. Ceci réduit les effets des porteurs chauds et améliore la mobilité effective dans le canal, donc augmente le courant de saturation

II.5.3. l'effet de latch-up sur le SOI, ou le thyristor parasite. L'effet de latch-up est un phénomène qui induit le déclenchement du thyristor parasite représenté (Figure II.3) par deux transistors bipolaires NPN et PNP dans les technologies CMOS sur substrat massif. Le déclenchement du latch-up est lié à la proximité des zones N+ et P+ de transistors NMOS et PMOS voisins. Sur le SOI, ces zones sont complètement isolées et le claquage entre ces deux zones est impossible quelle que soit la distance qui les sépare.

Figure II.6: vue schématique de transistor BULK MOSFET vs SOI (latch-up)

II.5.4. Faible courant de fuite. Le courant de fuite associé aux jonctions drain/substrat et source/substrat est proportionnel à leur surface. Cette surface est diminuée en utilisant un substrat SOI car les jonctions planes de drain et de source sont éliminées à cause du contact avec l'oxyde enterré (Figure II. 6). Cette diminution du courant de fuite donne un avantage très important qui est la réduction de la consommation, qui constitue un avantage crucial pour les applications nomades et la durée de vie de la batterie

Figure II.7 : Courant de fuite de drain et de source pour un MOS sur substrat massif et un MOS SOI

II.5.5. Réduction de l'effet de canal court. La diminution de la longueur de canal des transistors MOSFET induit de nombreux effets, dont l'un est appelé effet de canal court. Il est dû aux zones de désertion de source et de drain qui viennent recouvrir partiellement celle de la grille, représentée par le trapèze Q g à la Figure II.8.

Figure II.8 : Schéma montrant l'effet de partage de charge

Pour les transistors à canal « long », cet effet est faible par rapport à la zone de contrôle de la grille, tandis qu'au fur et à mesure de la réduction de la longueur de la grille, cet effet devient de plus en plus significatif. L'effet de canal court s'explique par une perte de contrôle de la charge du canal par la grille, ce qui a pour conséquence de réduire la tension de seuil. Cet effet est très important pour les transistors MOSFET sur substrats massifs, mais dans le cas du SOI et en particulier pour les transistors totalement désertés, l'espace de charge dans le film de silicium reste très bien contrôlé par la grille. Comme conséquence, les effets de canal court sont réduits en comparaison des transistors MOSFET sur substrat massif Figure II.8.1

Figure II.8.1. : Distribution de la charge de désertion contrôlée par la grille (Qg) pour les Transistors à canal long (gauche) et à canal court (droite).

II.5.6. Augmentation de la densité d'intégration. La miniaturisation, sans augmenter les courants de fuite [3, 12]. Comme conséquence, de meilleures performances en termes de rapidité peuvent être obtenues à des tensions d'alimentation plus faibles. de tous les produits électroniques requiert la réduction des tailles des composants et l'accroissement de la densité d'intégration tout en gardant la même performance et la même durée de vie ou plus. L'utilisation d'un substrat SOI permet à la fois une isolation diélectrique verticale parfaite entre les différents composants (puissance, logique et analogique), grâce à la couche diélectrique enterrée et une densité d'intégration plus importante.

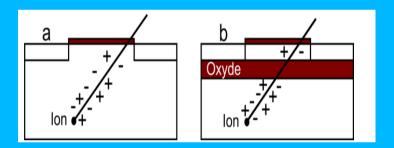

II.5.7. Meilleure tenue aux radiations. Certaines applications comme l'aéronautique et l'espace sont soumis au rayonnement cosmique. Des forts flux de particules chargées engendrent des «photo-courant» dans les circuits intégrés. Par ailleurs, une particule unique très ionisante (proton ou ion) produit le long de sa trace un plasma conducteur (Figure II.9) responsable d'effets isolés : claquages ou courts-circuits, tous deux destructifs ; basculement d'un point mémoire ou erreur dans un circuit logique, non destructifs mais entraînant des erreurs graves au niveau système.

Figure II.9: Effet des irradiations (a) sur substrats massifs et (b) sur MOS SOI.

Le durcissement vis-à-vis de ces effets est obtenu principalement par la réduction du volume de silicium contenant les composants. L'utilisation de fines couches actives de silicium minimise l'impact des radiations ionisantes sur les performances des composants .La technologie de PDSOI et FDSOI, en particulier concernant la haute fréquence de fonctionnement, le faible courant de fuite et la réduction de l'effet de canal court.

II.5.8. Réduction des capacités parasites. Par la seule présence de l'oxyde enterré, les capacités parasites sont considérablement réduites. Les capacités de jonction source-substrat et drain-substrat, qui correspondent à la capacité d'une jonction polarisée en inverse pour le MOSFET bulk, ne sont en réalité pour le SOI qu'une capacité d'oxyde CBox. Le transistor SOI présente, toujours par comparaison au transistor BULK MOS, un canal de conduction plus

mince et isolé, une simplification des niveaux d'interconnexions au-dessus des transistors du fait de l'absence des caissons. Lorsque le film de silicium est faiblement dopé, voire non dopé, il peut être entièrement déplété à tension Vg nulle, ce qui est également avantageux en ce qui concerne le courant de percement en surface.

II.5.9 Pente inverse sous le seuil Ce qu'on appelle dans la littérature « pente inverse sous le seuil » se définit comme l'inverse de la pente de la caractéristique Id en fonction de Vgs, dans la zone où la tension est inférieure à la tension de seuil Vth. C'est un courant de diffusion de porteurs minoritaires, puisque la couche d'inversion du canal n'est pas encore formée. Il contribue à la puissance statique consommée par les circuits numériques, c'est-à-dire la puissance consommée à l'état de veille. Il a été montré que les transistors MOSFET sur SOI ont une pente inverse sous le seuil plus faible que sur substrat massif, permettant d'utiliser des tensions de seuil plus faibles

II.6. Les inconvénients de transistor MOS SOI .La technologie SOI a beaucoup d'avantages, mais elle a aussi certains inconvénients qui limitent son utilisation généralisée.

**II.6.1**. **L'effet du transistor bipolaire parasite.** Il est du à l'ionisation par impact et aux charges qui s'accumulent dans le substrat augmentant le potentiel du film, polarisant ainsi en direct la jonction film de Silicium- source. Ce qui active un transistor bipolaire parasite en parallèle avec le MOSFET. Ce courant parasite peut empêcher le transistor de commuter de l'état ON à l'état OFF (verrouillage ou Latch-up du MOSFET).

**II.6.2.** Coût des plaquettes. Malgré les nouvelles techniques de fabrication performantes des plaquettes SOI, cette technologie reste plus chère par comparaison à celle sur substrat massif, car elle nécessite plus de matériau (wafer bonding) et plus d'étapes technologiques. A titre d'exemple, selon Virginia Semi-conductor, le prix d'une plaquette SOI de 100 mm de diamètre, 400 μm d'épaisseur et dopée au bore est égal à 175 \$ par plaquette, alors que le prix d'une plaquette de silicium de 100 mm de diamètre, 500 μm d'épaisseur et dopée au bore varie entre 36 \$ et 80 \$ suivant la résistivité du silicium.

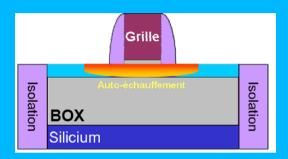

**II.6.3.** Conductivité thermique. Dans l'utilisation d'un SOI, la présence de la couche d'oxyde enterrée empêche la dissipation thermique par la face arrière du substrat et peut alors poser un problème d'auto échauffement pour les composants de puissance. En effet, il y a une grande différence entre les conductivités thermiques du silicium et celle de l'oxyde

À cause de la faible conductivité thermique de l'oxyde enterré (100 fois plus faible que celle du silicium) dans les transistors MOS SOI, la chaleur produite dans le film SOI est relativement difficile à évacuer. Il est plus prononcé dans les canaux courts à cause du courant élevé et du faible volume de Silicium. Le remplacement du SiO<sub>2</sub> de l'oxyde enterré par de l'Alumine ou tout autre diélectrique à forte conductivité thermique améliorera l'évacuation de la chaleur vers le substrat de silicium, ce qui réduira l'auto échauffement.

Figure II.10: Auto échauffement dans un transistor MOS SOI à isolant SiO2

Malgré l'évacuation de la chaleur plus difficile, les composants et les circuits sur substrat SOI présentent trois avantages majeurs pour un fonctionnement à haute température par rapport aux substrats massifs : absence de « *latchup* » activé thermiquement, réduction des courants de fuite et, pour les composants totalement désertés, faible variation de la tension de seuil avec la température

#### II.7. Fabrication d'une plaquette SOI

Le procédé de fabrication des composants sur SOI est proche de celui sur substrat massif, à l'exception des substrats de départ. Il existe plusieurs méthodes pour réaliser une plaquette SOI, chacune a ses avantages et ses inconvénients. On peut les classer en trois grands groupes de techniques : techniques de collage, techniques d'épitaxie et technique de la conversion du matériau (figureII.11)

Figure II.11: Différentes techniques de réalisation d'une plaquette SOI

**II.7.1. Technique de collage.** Cette technique dite aussi wafer bonding en anglais est divisée en plusieurs technologies.

#### a)BESOI (Bonded and Etch back SOI).

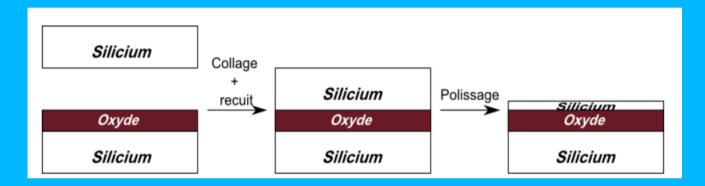

Cette technique consiste à coller deux plaquettes de silicium, dont l'une a une surface oxydée, par les forces de Van der Waal ou liaisons hydrophiles entre les deux surfaces, puis à effectuer un recuit à 1100°C. Cette étape est suivie par un polissage mécano-chimique jusqu'à l'obtention de l'épaisseur de silicium désirée, (Figure II.12).

Cette méthode est simple, mais elle a un inconvénient majeur, qui est son coût, puisqu'on a besoin de deux plaquettes de silicium pour obtenir une seule plaquette SOI.

Figure II.12 : Etapes du procédé BESOI

#### b) SmartCut

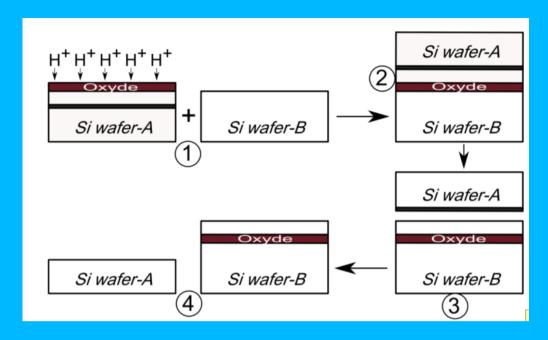

Ce procédé, est basé sur le même principe de collage de deux plaquettes de silicium. La différence est l'utilisation des ions hydrogènes implantés dans la plaquette supérieure. Donc on utilise cette fois une plaquette de silicium à surface oxydée et implantée par des ions hydrogènes, où la profondeur est fixée par l'énergie d'implantation. Cette plaquette est collée à une autre par liaisons hydrophiles puis un recuit est réalisé. La première phase de ce recuit, de 400 à 600°C, permet de faire coalescer les microcavités dues à L'implantation, et permettent ainsi la propagation d'une fissure à travers toute la couche implantée d'ions hydrogènes (Figure II.13). La seconde phase du recuit, au dessus de 1000°C, aide à consolider les liaisons chimiques entre les deux surfaces collées. Après séparation, la rugosité de surface du silicium sur oxyde est rectifiée par un polissage. Le reste de la plaquette donneuse est intact et peut être recyclé pour former une autre plaquette SOI, ce qui diminue le coût de fabrication par rapport au procédé BESOI utilisant deux plaquettes.

Figure II.13 : Principales étapes du procédé Smart-Cut

#### II.7.2. Technique d'Epitaxie.

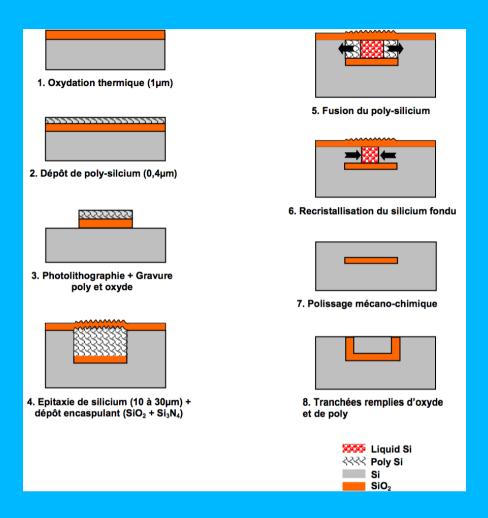

Le LEGO (Lateral Epitaxial Growth over Oxide) est une technique basée sur la fusion et la recristallisation de motifs épais de silicium poly-cristallin sur oxyde, et qui permet d'obtenir des motifs localisés de SOI sur un substrat de silicium par la technique de photolithographie. Elle a été développée en premier lieu dans les années 80 et a été désormais reconsidérée à cause d'un nouveau marché pour les structures SOI partielles à faible coût, celui de l'intégration de composants de commande et de puissance sur une même puce avec une isolation diélectrique efficace. La (Figure II.13) présente les étapes du procédé LEGO.

Figure II.13 : Etapes du procédé LEGO

#### II.7.3. Technique de conversion du matériau.

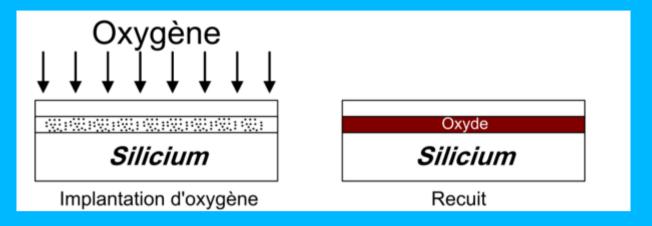

SIMOX (Separation by implantation of oxygen) Cette technique consiste à implanter des ions d'oxygène afin d'obtenir la couche d'oxyde. La dose et l'énergie d'implantation permettent de déterminer la profondeur et l'épaisseur de la future couche d'oxyde (Figure II.14) Après implantation, de nombreux défauts (dislocations et fautes d'empilement) sont générés dans la couche supérieure de silicium. Un recuit à très haute température (1300°C) pendant quelques heures ou 1405°C pendant 30 minutes) est donc nécessaire pour rétablir une qualité cristalline acceptable de la couche SOI ainsi que pour lier les atomes d'oxygène avec les atomes de silicium en une couche bien délimitée de SiO2 Enterré (Figure II.14)

Figure II. 14: Etapes technologiques de la technique SIMOX

#### **Conclusion**

Dans ce deuxième chapitre on a introduit un aperçu de l'évolution de la technologie MOS SOI .puis on a représenté les deux types de transistor PD et FD suivie d'une comparaison entre MOS SOI et Bulk MOSFET, les différentes technique de fabrication d'une plaquette MOS SOI ,La technologie SOI présente d'innombrables avantages. Cependant, son inconvénient majeur, surtout en ce qui concerne le PDSOI, est l'importance des effets canaux courts.

En effet la polarisation du drain peut induire des effets canaux courts par influence électrostatique à travers l'oxyde enterré. Cet effet néfaste n'est pas à négliger lorsque l'épaisseur de l'oxyde est importante. Naturellement, réduire l'épaisseur d'oxyde ne ferait que réduire l'influence électrostatique, en revanche, insérer une grille en-dessous de l'oxyde constituerait un bouclier qui bloquerait complètement les lignes de champs. Ceci permettrait directement de protéger le canal et de réduire les effets canaux courts. Cette structure, permettant ainsi d'insérer une seconde grille est appelée structure double grille dite DGFET transistor, Le double-grille (DG) rentre dans le cadre des structures multi-grilles. [II.4] se qui a donner naissance au structure multi-grille comme solution pour continuer à augmenter les performances des dispositifs.

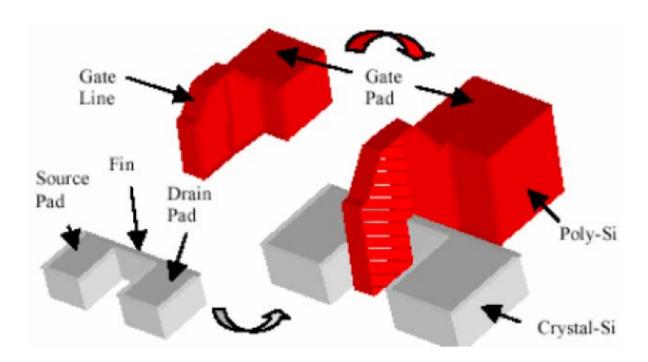

# III .Les transistors à grilles multiples

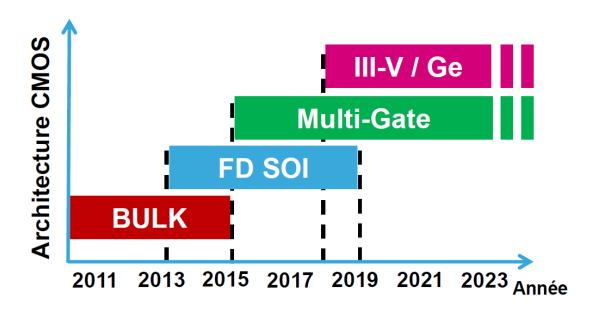

Les transistors à grilles multiples (MUGFETs) sont largement reconnus comme des candidats prometteurs pour satisfaire les exigences de l'ITRS, grâce au bon contrôle du canal par la grille. La première publication décrivant un transistor SOI MOSFET double grille par T.Sekigawa and Y. Hayashidate en 1984 [II.2]. Le composant a été nommé « XMOS », car sa section efficace ressemble à la lettre grecque  $\Xi$  (Xi), en utilisant cette configuration un m la Figure au dessous illustre les prédictions de l'ITRS en 2011 sur les architectures CMOS en fonction des annonces des industriels. INTEL, par exemple, a annoncé en 2011 l'utilisation des transistors FinFET pour la fabrication de ses futurs microprocesseurs dans le nœud technologique 22 nm [I]. En 2012, Intel a commercialisé ses produits dans les applications hautes performances en utilisant l'architecture Trigate 22 nm [I].

Figure III: Prédiction de l'ITRS 2011 de l'utilisation des différentes architectures CMOS en fonction de l'année.[III.I]

Depuis, plusieurs architectures à grilles multiples ont vu le jour. Les dispositifs sont considérés parmi les architectures les plus innovantes, les plus prometteuses pour les générations technologiques les plus intégrées. Un transistor double-grille est équivalent à une structure SOI dans laquelle l'oxyde de grille et l'oxyde enterré ont la même épaisseur, les grilles avant et arrière étant connectées ensemble. D'un point de vue électrostatique, le transistor MOS SOI double-grille est plus robuste que le transistor MOS à une simple grille puisque la double-grille, fortement couplée au canal, contrôle simultanément le potentiel de

surface aux deux interfaces du film du silicium.Par conséquent, les effets de canaux courts sont réduits. Un autre avantage de ces dispositifs vient du caractère symétrique de la distribution du potentiel électrostatique qui induit un champ nul au milieu du film ce qui permet d'augmenter la mobilité.

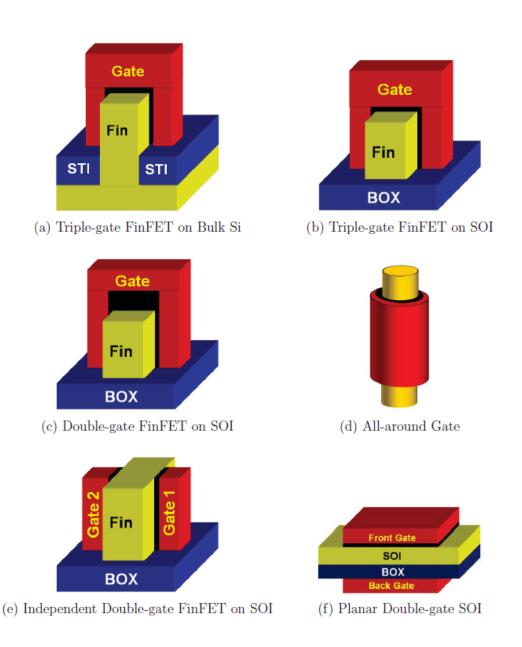

Les différentes structures des grilles qui contrôle le canal et leur positionnement autour du film de silicium qui détermine la dénomination des diffère structure MOS SOI sont représentées dans la figure III.

Figure III.I : Les Différents structures de la grille SOI

#### III.1 Avantages des transistors à grilles multiples

L'avantage majeur des dispositifs multi-grilles est la réduction des effets canaux courts. Puisque le canal est contrôlé par la grille de plusieurs côtés, on a un meilleur contrôle électrostatique du canal par la grille contrairement aux structures de transistors conventionnelles. Ceci a pour conséquence de réduire les courants de fuites. Aussi, grâce aux, dimensions de ces dispositifs, la réduction des coûts à travers la miniaturisation peut donc se poursuivre. Un deuxième avantage de ces dispositifs est l'amélioration du courant débité à l'état passant du transistor (ION) et donc une augmentation de la vitesse du circuit grâce à la réduction du canal de conduction, donc les performances sont nettement améliorées avec de telles architectures multi-grilles. A cet effet, elles font l'objet actuellement de recherches intenses dans de nombreux laboratoires de la microélectronique [II.I].

# III.2. La technologie MOS SOI double-grille.

# III.2.1. Introduction au transistor mos soi double grille.

De nombreuses solutions sont actuellement étudiées pour contourner les limitations technologiques liées à la réduction d'échelle du transistor MOS standard. Certaines de ces solutions incluent des modifications au sein des structures existantes, dans l'espoir de prolonger leur miniaturisation. Selon le rapport de l'ITRS, le transistor MOS à double-grille appelé DGFET (figure II.2) est identifié comme l'un des candidats les plus prometteurs pour les futurs circuits intégrés à très grande densité d'intégration. Ceci est essentiellement dû à son aptitude intrinsèque à suivre la tendance continuelle de miniaturisation des dispositifs (grâce au contrôle du canal par les deux grilles).En parallèle et afin de satisfaire aux exigences du concepteur de circuits, il est nécessaire de développer des modèles compacts de ces technologies émergentes, précis, simples, efficaces en termes de temps de calcul, contenant un minimum de paramètres et enfin, prédictifs. Les travaux se positionnent depuis quelques années dans le cadre de la modélisation compacte du transistor MOS à grilles multiples [II.1].

figure III.2 transistor double grille MOS

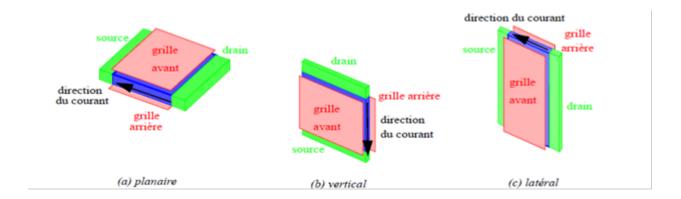

Les transistors MOS double-grille (DG) sont regroupés en trois catégories suivant la direction du transport électronique et la direction du champ de grille par rapport au plan du substrat qui est le plan horizontal. . Toutefois, l'agencement des grilles par rapport au canal constitue la différence entre ces MOSFET SOI. On parle alors :

- 1) le transistor double grilles planaire (linaire a) dont le transport des porteurs se fait parallèlement au plan du substrat et le champ électrique entre les deux armatures des grilles est perpendiculaire.

- 2) le transistor double grille non planaire (vertical b) dans lequel le champ et le transport des porteurs se font parallèlement au substrat

- 3) le transistor double grille quasi-planaire où le champ et transport dépendent de l'agencement des grilles (latéral) de type FinFET et leurs dérivées, dans lesquels, seule la zone active se trouve dans le plan vertical par rapport au substrat. La source et le drain restent dans le plan horizontal comme pour un transistor planaire conventionnel et le transport électronique et le champ de grille sont parallèles au plan de substrat

Figure III.4.Description des trois catégories d'architecture de transistor double-grille : (a) conduction planaire (b) conduction verticale (c) conduction latérale (FinFET)

Ces trois catégories de double-grille possèdent des particularités technologiques « telles qu'une résolution lithographique et un alignement des grilles » totalement différentes. En conséquence de ces différences du point de vue technologique, les propriétés électriques demeurent nettement modifiées lorsque nous passons d'une catégorie à une autre. Nous allons dans ce qui suit présenter les points essentiels de ces trois structures DGFET. [II.7]

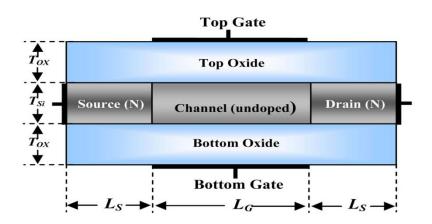

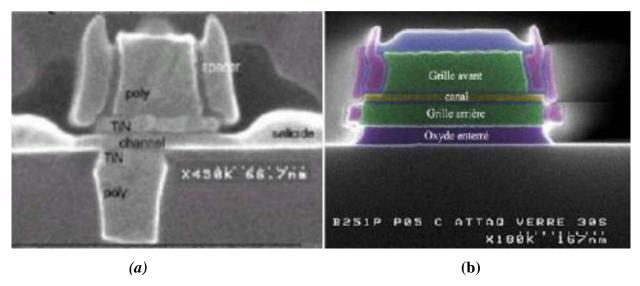

### III.2.2. Le transistor double grilles planaire (linaire).

L'architecture du MOSFET double-grille planaire est basée sur celle du SOI à une grille. L'oxyde enterré est placé sur un second empilement de grilles. Ces dispositifs ne nécessitent pas de résolution lithographique inférieure à la longueur de grille Lg car le procédé « *smart cut* » permet sans lithographie de réaliser des couches actives ultraminces(<10nm).

Les grilles des transistors MOS SOI double-grille planaires réalisés à l'heure actuelle ne sont pas parfaitement alignées. En effet, ces grilles sont gravées successivement et sont alignées «optiquement». L'imprécision tenant au non alignement des grilles génère une forte dispersion des caractéristiques des composants à canaux courts. Ceci constitue malheureusement un frein à la production en grande série. Lorsque la grille inférieure recouvre un des caissons, cela génère des capacités parasites qui dégradent les performances électriques. Lorsque le non-alignement est très important, comme il est décrit dans (la Figure II.5-a), le dispositif se comporte comme s'il ne possédait qu'une seule grille active. Cependant et d'une manière générale, les structures présentant de faibles non alignements

des grilles (Figure II.5-b) restent très performantes. Pour fabriquer les transistors ultimes, la réalisation du MOSFET double-grille planaire auto-aligné est indispensable mais technologiquement complexe [Birahim Diagne]

Figure II.5 Image au MEB (microscope électronique à balayage) d'une coupe de Transistor MOS double-grille (a) non-auto-alignée et (b) auto-alignée

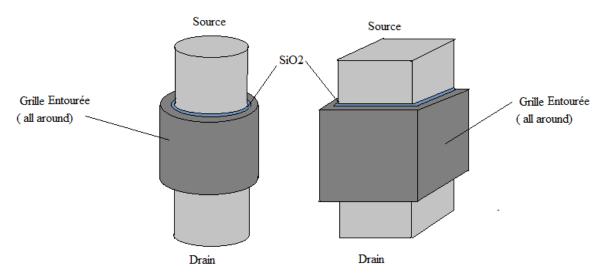

#### III.2.3. Transistor Gate All Around (GAA).

L'architecture Gate All Around (GAA) est un autre type d'architecture multi grille planaire. Le principe de ce dispositif consiste à entourer totalement le canal de conduction pour un meilleur contrôle électrostatique et donc de lutter efficacement contre les effets de canal court .La réalisation technologique d'un tel transistor est extrêmement complexe. néanmoins, STMicroelectronics a développé un procédé innovant pour la fabrication de transistor GAA en utilisant la technologie Silicon On Nothing (SON). [III.6].

Dans cette structure, il existe une possibilité intéressante pour donner a la grille une forme entourant ou cylindrique, dans laquelle la section transversale de la chaîne de silicium a une forme cylindrique et l'électrode de grille complètement entoure la région de canal dispositif. Le courant circule verticalement le long de la Si/SiO2 cylindrique interface et la longueur de grille du transistor est définie par la hauteur du matériau de grille, qui, à son tour, peut être commandé soit par un dépôt de film ou par une gravure anisotrope à sec. Actuellement, la structure en grille entourant est utilisée principalement pour l'intégration de transistors à base

de nanofils pour adresser de la longueur de grille ultra-courte [III.8].

Figure III.6 Transistor MOSFET All Around [III.8]

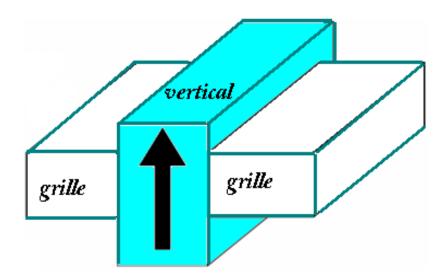

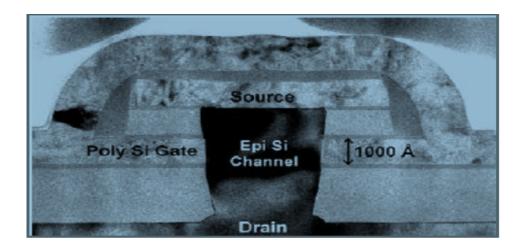

# III.2.4. Transistor double grille a conduction vertical.

Figure III.7 Orientation du transport électronique et effet de champ sur le MOS double grille vertical. (La flèche indique l'orientation du transport et la position des grilles indique la direction de l'effet de champ par rapport au plan supérieur du substrat qui correspond au plan horizontal)

L'avantage du transistor MOS double-grille vertical, dont une image TEM (microscopie par transmission électronique) est présenté à la Figure. II.8, réside dans le fait que la longueur des grilles n'est pas définie par lithographie. Cela permet d'atteindre dans la miniaturisation

des longueurs de grille ultracourtes [III.I]. De plus, les grilles sont naturellement autoalignées

Figure. III.8. Image au MEB d'un transistor vertical à grille enrobante (Lg = 100nm) [III.I]

#### **II.2.5 Transistor DELTA-FET**

La Fabrication d'un transistor MOSFET DG auto-alignée a été le but des ingénieurs et des chercheurs depuis qu'il a été proposé par Sekigawa et Hayashi en 1984, Le premier model auto-aligné verticale multi-grille du MOSFET a été appelé DELTA (canal Lean Fully Depleted Transistor). Ce dispositif a été proposé par D. Hisamoto et al. en 1989. La figure II.11 présente une section transversale de la DELTA MOSFET.

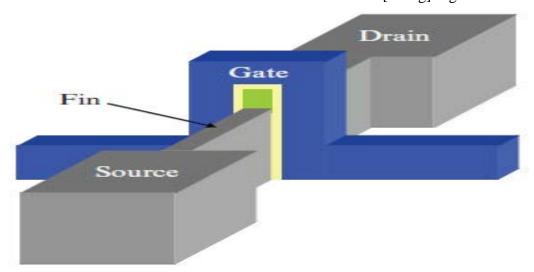

# **III.2.6 transistor FinFET**

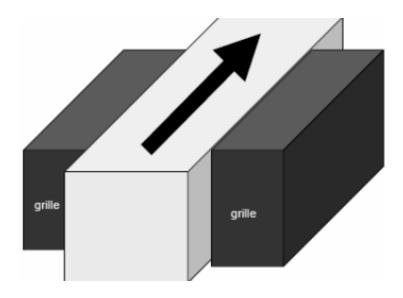

Figure III.9 Orientation du transport électronique et effet de champ sur mos soi DG

# quasi-planaire

Les transistors double-grille planaires et à conduction verticale ne sont pas facilement intégrables dans la filière CMOS. Un nouveau type d'architecture plus proche de la technologie MOS classique a été étudiée : les transistors à conduction latérale ce type d'architecture appelée transistor MOS double-grille quasi-planaire (FinFET). Il tire son nom de son canal en forme d'aileron (*Fin*). La première mise en œuvre de dispositifs FinFET a été publiée en 1980, par D. Hisamoto et al. [livre amara amara dg]. Ce transistor a été initialement nommé DELTA et a été renommé FinFET en 1999 [a a dg]. Figure II.7

Figure III.10 Schémas d'un transistor mos soi double grille FinFET

.

Les étapes de réalisation d'un tel dispositif sont schématisées sur la Figure III.11. La zone active (en forme d'aileron ou de mur) et les caissons source et drain commencent par être dessinés. L'oxyde et le contact de grille sont ensuite déposés autour de l'aileron puis gravé.

Figure III.11: Schéma d'une structure FinFET quasi-planaire

# Conclusion

Dans ce chapitre on a présenté les différentes architectures de transistors MOSFETs SOI à grilles multiples (MG-FET) L'avantage majeur des dispositifs multi-grilles est la réduction des effets canaux courts. Puisque le canal est contrôlé par la grille de plusieurs côtés, on a un meilleur contrôle électrostatique du canal par la grille contrairement aux structures de transistors conventionnelles. Ceci a pour conséquence de réduire les courants de fuites.

#### **IV Introduction**

Durant ces dernières années, et cause des couts élevés de l'expérimentation, les chercheurs se sont orientes vers la simulation. Ce type de simulation permet en effet de déterminer, en tout point du volume d'un composant, les densités de porteurs, électrons et trous, les énergies les taux de recombinaison, les champs électriques et autres paramètres qui s'en déduisent comme les courant, capacités, etc .

Il existe principalement quatre types de simulateurs nous citons à titre d'exemple, les simulateurs fonctionnels ou logiques les simulateur électriques ou analogique, les simulateurs technologiques et ceux des composants ou des dispositifs citons AFORS-HET,PC1D ADS, GENESYS IC –CAP, ORIEL,PVSYST, SILVACO, La simulation de dispositif à l'aide de ses différents simulateurs permet de comprendre le comportement de ces dispositifs en fonction des paramètres tels que le dopage et les épaisseurs des régions, afin de mieux comprendre les phénomènes physiques et géométrique internes existant, dans ce chapitre on s'intéresse au l'outil de simulation TCAD SILVACO.

#### IV.1. L'outil de simulation – SILVACO

L'environnement SILVACO est largement exploité, tant dans l'industrie que dans les laboratoires de recherche .SILVACO (Silicon Valley Corporation) est une société Américaine, « Silvaco International» ayant son siège à Santa Clara en Californie. Elle est un des principaux fournisseurs de chaînes professionnelles de logiciels de simulation par éléments finis et de conception assistée par ordinateur pour les technologies de l'électronique TCAD (Technology Computer Aided Design). Ces outils sont employés par les compagnies de microélectronique dans le domaine de la recherche, du développement et de la conception de dispositifs. Le développement de SILVACO, les ventes et les équipements de soutien sont stratégiquement localisés dans le monde entier pour soutenir la clientèle. Une majeure partie du modèle des affaires de SILVACO se fonde sur la capacité de la compagnie à fournir des ingénieurs technico-commerciaux bien formés et expérimentés pour le support à la clientèle sur place dans toutes les régions principales de fabrication de semi-conducteurs .

Historiquement la compagnie a été fondée en 1984 par Dr. Ivan Pesic pour répondre aux besoins des designers de circuits intégrés analogiques pour des modèles SPICE (Simulation Program with Integrated Circuit Emphasis) de plus en plus précises et linéaires.

Le produit initial a été le système d'extraction des paramètres UTMOST (Universal Transistor Modeling SofT ware) qui est devenu un standard industriel pour l'extraction des paramètres, la caractérisation des dispositifs et la modélisation. L'entrée de SILVACO dans la technologie TCAD a eu lieu en 1989, et elle a été basée sur une recherche du Département des Dispositifs Physiques de l'Université de Stanford, ainsi apparaissent dans SILVACO « Athena » comme simulateur des processus et « Atlas » comme simulateur des dispositifs (2D et 3D).

A l'aide d'un projet de recherche de l'Université de California, Berkeley, en 1992 SILVACO a conçu son propre logiciel de simulation comportementale SPICE. Ainsi « SmartSpice » devient partie de la chaine TCAD de SILVACO, il permet des simulations des circuits électroniques avec les modèles physiques des composants crées à l'aide d'Atlas tout en utilisant une logique SPICE. « SmartSpice » écrit en C++ permet facilement l'introduction des modèles nouveaux de simulation et permet une amélioration des algorithmes numériques pour une meilleure convergence.

En 1997 SILVACO introduit IC CAD (Integrated Circuit Computer Aided Design) analogue qui est un outil pour capture schématique (schematic capture), disposition sur circuits imprimés (layout) et vérification physique. L'ensemble de ces outils avec le simulateur des circuits « SmartSpice» fournit une structure complète, à faible coût et d'une très grande productivité pour la conception des circuits intégrés analogiques.

En 2004 enfin, SILVACO propose un outil d'extraction de signaux parasites qui permet la conversion directe des données des masques et des informations intéressantes aux processus des schémas électriques (netlists). Sur cet ensemble complet de simulation TCAD, nous avons utilisé la partie dénommée « Atlas » pour simuler les modèle bidimensionnel d'un transistor MOSET SOI complètement deplete et MOSFET SOI partiellement deplete,

# IV.2. Présentation du paquet des programmes SILVACO

#### IV.2.1. Les outils de simulation ATLAS (de la société SILVACO)

Le logiciel de simulation ATLAS est un simulateur de modélisation bidimensionnelle décomposant, il permet la résolution des équations différentielles issues de la physique du composant comme celles de la diffusion ou du transport pour des géométries discrètes il est

donc capable de prédire les caractéristiques électriques de la plupart des composants semiconducteurs en régime continu, transitoire ou fréquentiel.

En plus du comportement électrique "externe", il fournit des informations sur la distribution interne de variables telles que les concentrations des porteurs, les lignes de courant, le champ électrique ou le potentiel, etc, autant de données importantes pour la conception et l'optimisation des procédés technologiques. Ceci est réalisé en résolvant numériquement l'équation de Poisson et les équations de continuité des électrons et des trous en deux dimensions en un nombre fini de points formant le maillage de la structure défini par l'utilisateur ou par le programme. Ce simulateur est composé de deux parties :

1-une partie traitement numérique (méthode d'intégration, de discrétisation...),

- 2- une partie formée des modèles physiques des composants semiconducteurs les plus récents : modèles de recombinaisons, d'ionisation par impact, de mobilités, en température et statistiques de Fermi-Dirac et de Boltzmann notamment. ATLAS a été conçu de façon à pouvoir utiliser d'autres outils qui facilitent son utilisation. Ces outils sont les suivants :

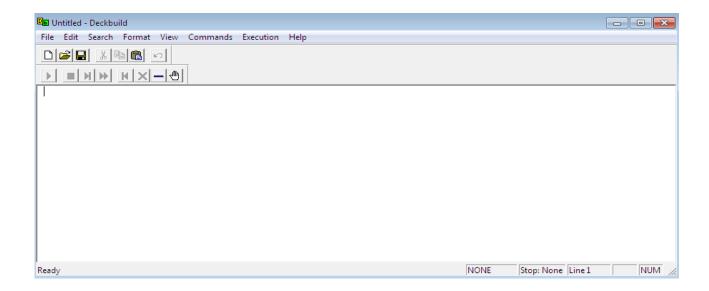

- **DEVEDIT:** environnement où est dessinée la structure des dispositifs (dimension, dopage, ...) et son maillage, Il peut être employé pour produire une nouvelle maille sur une structure existante, pour modifier un dispositif ou pour créer un dispositif à partir de zéro. Ces dispositifs peuvent alors être employés par les simulateurs 2D et 3D de SILVACO. DEVEDIT peut être employé par une interface utilisateur graphique (GUI abréviation de Graphics User Interface) ou comme simulateur sous DECKBUILD.

- **DECKBUILD**: environnement où est défini le programme de simulation. La structure et son maillage peuvent également être définis dans Deckbuild, C'est un environnement où on peut inviter les simulateurs, à tour de rôle, pour définir le programme de simulation : La structure, le maillage et les calculs électriques nécessaires peuvent également être définis dans DECKBUILD.

Figure IV : fenetre de Deckbuild

- TONYPLOT: environnement où sont visualisés les résultats des simulations (structure du composant, distributions de grandeurs diverses dans celui-ci, caractéristiques électriques...). Tonyplot puissant outil, est donc conçu pour visualiser les structures 1D et 2D produits par les simulateurs de SILVACO, Il fournit également beaucoup de fonctions spécifiques de visualisation de TCAD telles que les lignes de la coupe 1D, l'animation des marqueurs pour exposer la variation des vecteurs, intégration des fichiers de données 1D ou les fichiers (.log). Il y a aussi un autre outil similaire à celui-là, sauf qu'il conçu pour visualiser les structures 3D, nommé TonyPlot3D.

- MASKVIEW : éditeur de layout.

- **OPTIMIZER**: optimise les paramètres de la structure de façon à obtenir en final la valeur du paramètre que nous lui avons définie au préalable. Cet outil permet donc l'optimisation pour la calibration des simulateurs de processus et de dispositifs. Il permet donc d'ajuster ajustage automatiquement les paramètres électriques ou les paramètres du processus en jouant sur un ou plusieurs paramètres d'entrée.

#### IV.2.2. Présentation d'Atlas

Le logiciel de simulation ATLAS est un simulateur de modélisation bidimensionnelle ou 3d de composants. Basé sur la physique du semiconducteur, Il prédit le comportement électrique des structures semi-conductrices spécifiées et fournit des aperçus de mécanismes

physiques internes associés au fonctionnement des dispositifs. Atlas est capable de prédire les caractéristiques électriques de la plupart des composants semiconducteurs en régime continu, transitoire ou fréquentiel. En plus du comportement électrique "externe", il fournit des informations sur la distribution interne de variables telles que les concentrations des porteurs, les lignes de courant, le champ électrique ou le potentiel, etc., autant de données importantes pour la conception et l'optimisation des procédés technologiques. Ceci est réalisé en résolvant numériquement l'équation de Poisson et les équations de continuité des électrons et des trous en deux dimensions en un nombre fini de points formant le maillage de la structure défini par l'utilisateur ou par le programme. Ce simulateur est composé de deux parties :

- Une partie traitement numérique (méthode d'intégration, de discrétisation...).

- Une partie formée des modèles physiques des composants semiconducteurs les plus récents: modèles de recombinaisons, d'ionisation par impact, de mobilités, en température et statistiques de Fermi-Dirac et de Boltzmann notamment.

ATLAS a été conçu de façon à pouvoir utiliser les autres outils qui facilitent son utilisation tel que : ATHENA, DEVEDIT, TONYPLOT, DECKBUILD.

ATHENA, permet de simuler les processus de fabrication des composants intégrés. C'est un simulateur des procédés de fabrication et simulateur de composants. Il permet de simuler les étapes d'implantation d'ions, de dépôt, de gravure, de recuit et d'oxydation.

En conclusion on peut dire qu'Atlas peut être utilisé autonome ou comme un outil noyau dans le milieu de simulation VWF (Virtual Wafer Fabrication) de SILVACO. Dans le but de prévoir l'impact des variables du processus sur le comportement du circuit [II.9]

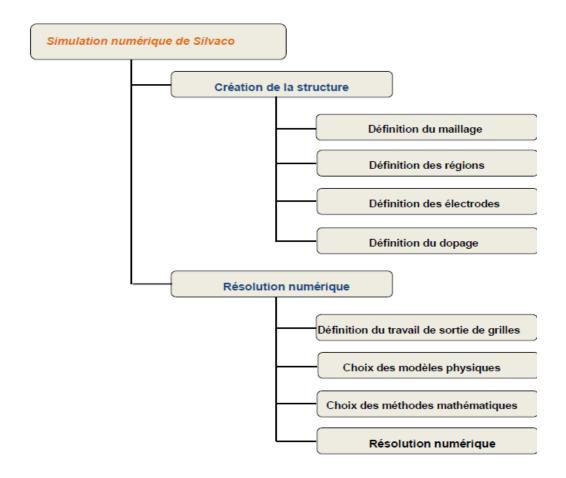

# IV.2.3. Logique de programmation [II.4]

Apres la présentation de la chaine progicielle TCAD de SILVACO, sa composition interne et le fonctionnement « d'Atlas » nous allons maintenant présenter l'ordre des commandes propres à la logique de programmation « d'Atlas ». Ainsi il existe cinq groupes de commandes, ces groupes doivent être organisés correctement. Si l'ordre n'est pas respecté, un message d'erreur apparaît et le programme ne s'exécute pas d'une façon correcte. Par exemple, si les paramètres ou les modèles de matériaux ne sont pas placés dans l'ordre idoine, le simulateur ne les prend pas en compte [I.4]

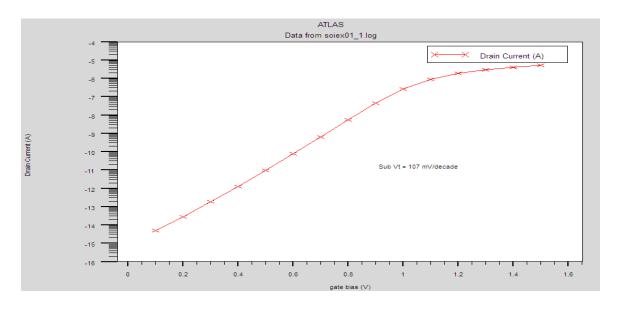

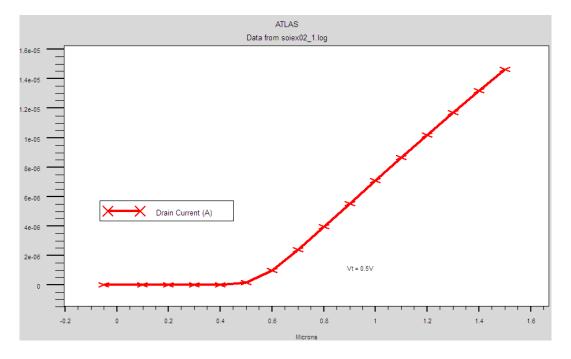

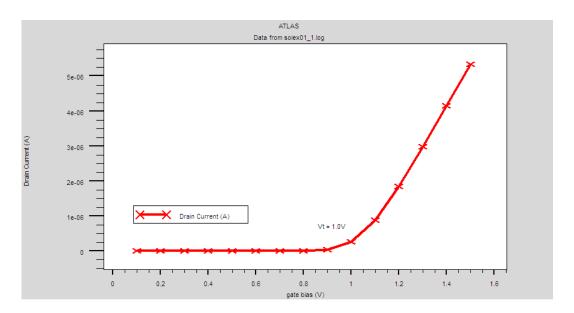

# IV.2.4. La simulation numérique d'une structure FD SOI déserté et PD SOI